The Alternate Instruction Set (AIS) is a second 32-bit instruction set architecture found in some x86 CPUs made by VIA Technologies. On these VIA C3 processors...

11 KB (1,002 words) - 05:08, 31 August 2024

The x86 instruction set refers to the set of instructions that x86-compatible microprocessors support. The instructions are usually part of an executable...

263 KB (14,911 words) - 15:01, 7 May 2025

Archived from the original on May 26, 2010. VIA, VIA C3 Processor Alternate Instruction Set Application Note, version 0.24, 2002 - see figure 2 on page 12...

9 KB (805 words) - 01:16, 14 April 2025

Centaur Technology. In addition to x86 instructions, VIA C3 CPUs contain an undocumented Alternate Instruction Set allowing lower-level access to the CPU...

11 KB (1,177 words) - 02:38, 9 May 2025

motherboards. In addition to x86 instruction decoding, the processors have a second undocumented Alternate Instruction Set. The Eden is available in four...

2 KB (145 words) - 09:12, 28 June 2024

indication signal line (AIS-L) Alarm indication signal path (AIS-P) Alternate Instruction Set, a second processor mode in Centaur/VIA C3 x86 CPUs Application...

3 KB (441 words) - 13:44, 5 August 2024

3DNow! instruction and PMULHRWC for the EMMI instruction. All VIA C3 processors support the VIA AIS (Alternate Instruction Set). The x86 instructions present...

98 KB (4,641 words) - 00:26, 21 March 2025

VIA Technologies Alternate Instruction Set, a CPU implementing a similar scheme to enter and exit into an alternate instruction set mode "8088 & V20"...

22 KB (1,303 words) - 22:26, 27 May 2025

CPUID (category X86 instructions)

differently: Bit 0: Alternate Instruction Set (AIS) present Bit 1: AIS enabled Bit 4: LongHaul MSR (MSR 0x110A) present Bit 5: FEMMS instruction (opcode 0F 0E)...

233 KB (13,261 words) - 20:43, 17 June 2025

The x86 instruction set has several times been extended with SIMD (Single instruction, multiple data) instruction set extensions. These extensions, starting...

133 KB (5,673 words) - 15:19, 3 June 2025

Some of the VIA x86 processors also contain an undocumented Alternate Instruction Set. By 1996, VIA established itself as an important supplier of PC...

14 KB (1,510 words) - 11:59, 15 June 2025

x86 instruction set which is a CISC design.[citation needed] In addition to x86, these processors support the undocumented Alternate Instruction Set.[citation...

13 KB (1,283 words) - 00:39, 15 May 2025

Instructional design (ID), also known as instructional systems design and originally known as instructional systems development (ISD), is the practice...

40 KB (4,092 words) - 20:56, 18 May 2025

Zilog Z80 (redirect from Z80 instruction set)

flags register, the Z80 introduced an alternate register set, two 16-bit index registers, and additional instructions, including bit manipulation and block...

118 KB (12,641 words) - 17:10, 15 June 2025

Alternate history (also referred to as alternative history, allohistory, althist, or simply A.H.) is a subgenre of speculative fiction in which one or...

81 KB (10,178 words) - 15:04, 13 June 2025

CPU cache (redirect from Instruction cache)

set associative L2 integrated cache 256 KiB in size, with 128-byte cache blocks. This implies 32 − 8 − 7 = 17 bits for the tag field. An instruction cache...

97 KB (13,324 words) - 06:26, 27 May 2025

RISC-V (category Instruction set architectures)

"risk-five": 1 ) is an open standard instruction set architecture (ISA) based on established reduced instruction set computer (RISC) principles. The project...

154 KB (15,964 words) - 13:28, 16 June 2025

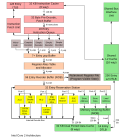

Microarchitecture (category Instruction processing)

organization and sometimes abbreviated as μarch or uarch, is the way a given instruction set architecture (ISA) is implemented in a particular processor. A given...

27 KB (3,576 words) - 18:07, 24 April 2025

reduced instruction set computing, and is also advantageous in embedded systems. The other advantage is that, because regular memory instructions are used...

17 KB (2,288 words) - 01:44, 18 November 2024

The PIC instruction set is the set of instructions that Microchip Technology PIC or dsPIC microcontroller supports. The instructions are usually programmed...

148 KB (4,299 words) - 09:55, 15 June 2025

Elliott 803 (section Instruction set)

each core. Instructions and data are based on a 39-bit word length with binary representation in 2's complement arithmetic. The instruction set operates...

35 KB (4,054 words) - 17:52, 31 March 2025

Power ISA (redirect from IBM Power Instruction Set Architecture)

Power ISA is a reduced instruction set computer (RISC) instruction set architecture (ISA) currently developed by the OpenPOWER Foundation, led by IBM...

23 KB (2,352 words) - 18:56, 8 April 2025

Hazard (computer architecture) (category Instruction processing)

design, hazards are problems with the instruction pipeline in CPU microarchitectures when the next instruction cannot execute in the following clock cycle...

10 KB (1,237 words) - 10:14, 13 February 2025

604, for example, has a two-way set-associative TLB for data loads and stores. Some processors have different instruction and data address TLBs. A TLB has...

25 KB (3,339 words) - 23:39, 2 June 2025

Microcode (redirect from Micro-instructions)

the programmer-visible instruction set architecture of a computer.[page needed] It consists of a set of hardware-level instructions that implement the higher-level...

74 KB (8,809 words) - 14:24, 16 June 2025

of registers that are directly encoded as part of an instruction, as defined by the instruction set. However, modern high-performance CPUs often have duplicates...

37 KB (1,811 words) - 15:31, 1 May 2025

alternation, or in true parallelism if there are enough CPU cores, ideally one core for each runnable thread. There are two approaches to instruction-level...

9 KB (1,026 words) - 00:26, 27 January 2025

X86 assembly language (section Instruction types)

through control flow instructions such as jumps, calls, and interrupts, which alter the flow of execution. FLAGS register: Contains a set of status, control...

57 KB (6,615 words) - 19:32, 6 June 2025

Millicode (category Instruction set architectures)

the instruction set of a computer. The instruction set for millicode is a subset of the machine's native instruction set, omitting those instructions that...

4 KB (404 words) - 15:29, 9 October 2024

and Magnetism (series) B&W series of shorts (30m each) 1957 titles: Alternating Current Theory / Capacitance / Coulomb's Law: Electrostatics / Coulomb's...

336 KB (283 words) - 01:46, 12 March 2025