computer central processing units (RISC CPUs) used a very similar architectural solution, now called a classic RISC pipeline. Those CPUs were: MIPS, SPARC...

24 KB (3,612 words) - 15:23, 17 April 2025

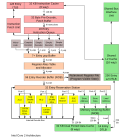

as well. The below example shows a bubble being inserted into a classic RISC pipeline, with five stages (IF = Instruction Fetch, ID = Instruction Decode...

4 KB (434 words) - 03:43, 12 March 2023

the terms Fetch, Decode, and Execute that have become common. The classic RISC pipeline comprises: Instruction fetch Instruction decode and register fetch...

21 KB (2,571 words) - 01:33, 10 July 2024

inserted between elements. Computer-related pipelines include: Instruction pipelines, such as the classic RISC pipeline, which are used in central processing...

15 KB (2,207 words) - 16:47, 23 February 2025

Hazard (computer architecture) (redirect from Pipeline break)

pipelined data path. Feed forward (control) Register renaming Data dependency Control dependency Hazard (logic) Hazard pointer Classic RISC pipeline § Hazards...

10 KB (1,237 words) - 10:14, 13 February 2025

Berkeley RISC Classic RISC pipeline, early RISC architecture CompactRISC, National Semiconductor family of RISC architectures MIPS RISC/os, a discontinued...

1 KB (208 words) - 13:28, 15 November 2024

parallelism within a single processor Classic RISC pipeline, a five-stage hardware based computer instruction set Pipeline (software), a chain of data-processing...

4 KB (537 words) - 02:27, 22 February 2025

(C-language Reduced Instruction Set Processor) design resembling the classic RISC pipeline, and which in turn grew out of the C Machine design by Bell Labs...

17 KB (1,878 words) - 03:33, 20 April 2024

Microarchitecture (section Instruction pipelining)

results out the other. Due to the reduced complexity of the classic RISC pipeline, the pipelined core and an instruction cache could be placed on the same...

27 KB (3,576 words) - 18:07, 24 April 2025

there to RISC-V International, a Swiss non-profit entity, in November 2019. Similar to several other RISC ISAs, e.g. Amber (ARMv2) or OpenRISC, RISC-V is...

150 KB (15,576 words) - 08:13, 22 April 2025

fetch, virtual-to-physical address translation, and data fetch (see classic RISC pipeline). The natural design is to use different physical caches for each...

97 KB (13,319 words) - 18:08, 30 April 2025

simultaneously. This section describes what is generally referred to as the "classic RISC pipeline", which is quite common among the simple CPUs used in many electronic...

101 KB (11,423 words) - 13:29, 23 April 2025

execute step happen. Time slice, unit of operating system scheduling Classic RISC pipeline Complex instruction set computer Cycles per instruction Branch predictor...

10 KB (1,255 words) - 07:48, 24 April 2025

System on a chip (section Pipelining)

They are frequently used in GPUs (graphics pipeline) and RISC processors (evolutions of the classic RISC pipeline), but are also applied to application-specific...

42 KB (4,733 words) - 14:48, 3 April 2025

Delay slot (section Pipelining)

leads to the classic RISC pipeline which completes one instruction every cycle. However, there is one problem that comes up in pipeline systems that can...

18 KB (2,471 words) - 13:21, 15 April 2025

S. Peter Song; Marvin Denman; Joe Chang (October 1994). "The PowerPC 604 RISC Microprocessor" (PDF). IEEE Micro. 14 (5): 13–14. doi:10.1109/MM.1994.363071...

24 KB (3,328 words) - 08:42, 3 April 2025

Instruction pipelining Pipeline stall Operand forwarding Classic RISC pipeline Hazards Data dependency Structural Control False sharing Out-of-order Scoreboarding...

17 KB (2,288 words) - 01:44, 18 November 2024

Reduced instruction set computer (redirect from RISC processor)

implementing an instruction pipeline, which may be simpler to achieve given simpler instructions. The key operational concept of the RISC computer is that each...

58 KB (6,885 words) - 16:35, 25 March 2025

implementations, as processor state is changed only in program order (see Classic RISC pipeline § Exceptions). Programs that experience precise exceptions, where...

14 KB (1,495 words) - 07:23, 10 August 2024

instruction types for a given benchmarking process. Let us assume a classic RISC pipeline, with the following five stages: Instruction fetch cycle (IF). Instruction...

6 KB (914 words) - 16:41, 2 October 2024

instructions, and macro-operation fusion. Reduced instruction set computer Classic RISC pipeline Eeckhout, Lieven (2010). Computer Architecture Performance Evaluation...

5 KB (729 words) - 15:29, 17 April 2025

Instruction pipelining Pipeline stall Operand forwarding Classic RISC pipeline Hazards Data dependency Structural Control False sharing Out-of-order Scoreboarding...

13 KB (1,583 words) - 11:03, 25 December 2024

scalar design that executed instructions in-order with a five-stage classic RISC pipeline. The microprocessor was partitioned into several blocks, the IBOX...

20 KB (2,627 words) - 16:56, 13 October 2024

to accelerate complex operations. In such systems, the ALUs are often pipelined, with intermediate results passing through ALUs arranged like a factory...

27 KB (3,326 words) - 00:30, 19 April 2025

Instruction pipelining Pipeline stall Operand forwarding Classic RISC pipeline Hazards Data dependency Structural Control False sharing Out-of-order Scoreboarding...

11 KB (1,739 words) - 05:02, 2 November 2024

ARM architecture family (redirect from Advanced RISC Machine)

as arm, formerly an acronym for Advanced RISC Machines and originally Acorn RISC Machine) is a family of RISC instruction set architectures (ISAs) for...

141 KB (13,693 words) - 20:19, 24 April 2025

Instruction pipelining Pipeline stall Operand forwarding Classic RISC pipeline Hazards Data dependency Structural Control False sharing Out-of-order Scoreboarding...

24 KB (2,892 words) - 18:54, 8 March 2025

complementing the R4600. The R4200 is a scalar design with a five-stage classic RISC pipeline. A notable feature is the use of the integer datapath for performing...

8 KB (985 words) - 12:36, 5 April 2025

MIPS (for Microprocessor without Interlocked Pipeline Stages), one of the projects that pioneered the RISC concept. Other principal founders were Skip...

47 KB (3,852 words) - 03:45, 8 April 2025

Marcel; Huynh, Huu Tue; Fortier, Paul (April 1993). "Systematic Design of Pipelined Recursive Filters". IEEE Transactions on Computers. 42 (4): 413–426. doi:10...

8 KB (1,031 words) - 20:28, 28 February 2025