Fast Cycle DRAM (FCRAM) is a type of synchronous dynamic random-access memory developed by Fujitsu and Toshiba. FCRAM has a shorter data access latency...

1 KB (145 words) - 02:06, 15 March 2024

Dynamic random-access memory (redirect from Fast Page Mode DRAM)

to as hyper page mode enabled DRAM, is similar to fast page mode DRAM with the additional feature that a new access cycle can be started while keeping...

92 KB (11,073 words) - 20:17, 11 July 2025

Memory refresh (redirect from DRAM refresh)

refresh time of 64 ms and 8,192 rows, so the refresh cycle interval is 7.8 μs. Generations of DRAM chips developed after 2012 contain an integral refresh...

22 KB (3,020 words) - 20:17, 17 January 2025

Synchronous dynamic random-access memory (redirect from Synchronous DRAM)

per clock cycle (single data rate). But this type is also faster than its predecessors extended data out DRAM (EDO-RAM) and fast page mode DRAM (FPM-RAM)...

81 KB (8,864 words) - 11:22, 1 June 2025

Random-access memory (section DRAM)

is generally faster and requires less static power than DRAM. In modern computers, SRAM is often used as cache memory for the CPU. DRAM stores a bit of...

58 KB (5,812 words) - 19:29, 20 July 2025

decays in seconds and thus must be periodically refreshed. SRAM is faster than DRAM but it is more expensive in terms of silicon area and cost. Typically...

27 KB (3,295 words) - 02:57, 12 July 2025

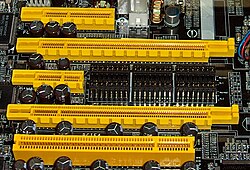

printed circuit boards (PCBs) designed to carry dynamic random-access memory (DRAM) chips. UniDIMMs can be populated with either DDR3 or DDR4 chips, with no...

7 KB (676 words) - 15:24, 17 March 2023

DRAM capacitor construction does. 1T-SRAM has speed comparable to 6T-SRAM (at multi-megabit densities). It is significantly faster speed than eDRAM,...

7 KB (840 words) - 16:27, 29 January 2025

set of timings is "faster" than another. For example, DDR3-2000 memory has a 1000 MHz clock frequency, which yields a 1 ns clock cycle. With this 1 ns clock...

9 KB (986 words) - 08:12, 12 July 2025

to occur at a faster rate. Used in the mid-1990s. EDO DRAM (Extended data out DRAM) – An older type of asynchronous DRAM which had faster access time than...

36 KB (3,551 words) - 15:24, 11 February 2025

speed specified by the preliminary DDR5 standard. The first production DDR5 DRAM chip was officially launched by SK Hynix on October 6, 2020. The separate...

24 KB (1,934 words) - 09:56, 18 July 2025

latency or CL, is the delay in clock cycles between the READ command and the moment data is available. In asynchronous DRAM, the interval is specified in nanoseconds...

17 KB (1,071 words) - 13:15, 15 April 2025

(FeRAM, F-RAM or FRAM) is a random-access memory similar in construction to DRAM but using a ferroelectric layer instead of a dielectric layer to achieve...

27 KB (3,212 words) - 23:19, 11 June 2025

signaling voltages, timings, and other factors. DDR3 is a DRAM interface specification. The actual DRAM arrays that store the data are similar to earlier types...

31 KB (3,266 words) - 15:40, 8 July 2025

EEPROM memory. Examples of volatile memory are dynamic random-access memory (DRAM) used for primary storage and static random-access memory (SRAM) used mainly...

29 KB (3,273 words) - 09:28, 5 July 2025

to mass-produce DRAM on a "10 nm-class" process, by which they mean the 1x nm node regime of 16 nm to 19 nm, which supports a 30% faster data transfer rate...

49 KB (4,577 words) - 06:47, 5 March 2025

the 386, small amounts of fast cache memory began to be featured in systems to improve performance. This was because the DRAM used for main memory had...

99 KB (13,735 words) - 12:24, 8 July 2025

the DRAM-framebuffer interface (up to 4MB), and clocking both the core and memory up to 80 MHz. In Windows, Virge was benchmarked as the fastest DRAM-based...

10 KB (1,234 words) - 21:04, 17 July 2025

DRAM once per clock cycle (to be precise, on the rising edge of the clock), and timing parameters such as CAS latency are specified in clock cycles....

6 KB (634 words) - 15:20, 16 July 2025

later SCPH-7000x): 86 mm², 53.5 million transistors) (combined EE+RDRAM+DRAM in SCPH-7900x ended with 65 nm CMOS design) CPU core: MIPS R5900 (COP0),...

34 KB (3,807 words) - 00:42, 8 July 2025

Solid-state drive (section DRAM and DIMM)

and later switching to dynamic random-access memory (DRAM). The STC 4305 was significantly faster than its mechanical counterparts and cost around $400...

127 KB (11,151 words) - 15:06, 16 July 2025

Flash memory (redirect from Program-erase cycle)

interface to flash memory chips differs from those of other memory types such as DRAM, ROM, and EEPROM, which support bit-alterability (both zero to one and one...

188 KB (17,263 words) - 13:26, 14 July 2025

completion of its first wafer fabrication unit ("Fab 1"), producing 64K DRAM chips. In 1984, the company had its initial public offering. Micron sought...

34 KB (2,789 words) - 06:48, 20 July 2025

universal memory. Currently, memory technologies in use such as flash RAM and DRAM have practical advantages that have so far kept MRAM in a niche role in the...

47 KB (5,352 words) - 05:49, 19 April 2025

latency for access – e.g. it can take hundreds of clock cycles for a modern 4 GHz processor to reach DRAM. This is mitigated by reading large chunks into the...

30 KB (4,140 words) - 20:24, 21 July 2025

the number of chip pins and board traces. Beginning with the Mostek 4096 DRAM, address multiplexing implemented with multiplexers became common. In a multiplexed...

31 KB (3,942 words) - 16:34, 26 July 2025

NRAM can theoretically reach performance similar to SRAM, which is faster than DRAM but much less dense, and thus much more expensive. Compared with other...

18 KB (2,419 words) - 02:45, 29 May 2025

paths, and their longer simple pipeline. Writes to main memory DRAM took tens of cycles to fully complete. But the R2020 chips queued and completed up...

5 KB (682 words) - 18:29, 21 July 2025

Direct memory access (redirect from Cycle steal DMA)

continued need for DRAM refresh (however handled) to monopolise the bus approximately every 15 μs prevented use of large (and fast, but uninterruptible)...

28 KB (3,924 words) - 17:05, 11 July 2025