Instruction-level parallelism (ILP) is the parallel or simultaneous execution of a sequence of instructions in a computer program. More specifically,...

9 KB (1,026 words) - 00:26, 27 January 2025

Parallel computing (redirect from Superword Level Parallelism)

different forms of parallel computing: bit-level, instruction-level, data, and task parallelism. Parallelism has long been employed in high-performance...

74 KB (8,380 words) - 19:27, 4 June 2025

form of instruction-level parallelism (ILP). However, ILP is often conflated with superscalar, the ability to execute more than one instruction at the...

4 KB (497 words) - 17:27, 30 July 2025

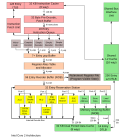

Central processing unit (redirect from Instruction decoder)

Modern CPUs devote a lot of semiconductor area to caches and instruction-level parallelism to increase performance and to CPU modes to support operating...

101 KB (11,434 words) - 05:49, 18 July 2025

In computer engineering, instruction pipelining is a technique for implementing instruction-level parallelism within a single processor. Pipelining attempts...

21 KB (2,571 words) - 18:01, 4 August 2025

In computer science, instruction scheduling is a compiler optimization used to improve instruction-level parallelism, which improves performance on machines...

10 KB (1,283 words) - 23:01, 5 July 2025

multiple-issue processor) is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In contrast to a scalar...

14 KB (1,678 words) - 19:56, 4 June 2025

Active message Instruction level parallelism Parallel programming model Prefix sum Scalable parallelism Segmented scan Thread level parallelism Some input...

16 KB (1,901 words) - 04:17, 25 March 2025

History of general-purpose CPUs (section Mid-to-late 1980s: Exploiting instruction-level parallelism)

methods are limited by the degree of instruction-level parallelism (ILP), the number of non-dependent instructions in the program code. Some programs can...

43 KB (5,891 words) - 13:30, 30 April 2025

Very long instruction word (VLIW) refers to instruction set architectures that are designed to exploit instruction-level parallelism (ILP). A VLIW processor...

24 KB (3,038 words) - 22:21, 26 January 2025

seek to exploit instruction-level parallelism with less hardware than RISC and CISC by making the compiler responsible for instruction issue and scheduling...

35 KB (4,329 words) - 19:12, 27 June 2025

Granularity (parallel computing) (redirect from Fine-grained parallelism)

amount of parallelism is achieved at instruction level, followed by loop-level parallelism. At instruction and loop level, fine-grained parallelism is achieved...

11 KB (1,487 words) - 00:23, 26 May 2025

are sent on a single TCP connection Instruction pipelining, a technique for implementing instruction-level parallelism within a single processor Pipelining...

759 bytes (126 words) - 13:25, 10 November 2023

Microarchitecture (category Instruction processing)

memory. One barrier to achieving higher performance through instruction-level parallelism stems from pipeline stalls and flushes due to branches. Normally...

27 KB (3,576 words) - 23:42, 21 June 2025

Bit-level parallelism is a form of parallel computing based on increasing processor word size. Increasing the word size reduces the number of instructions...

2 KB (314 words) - 22:33, 30 June 2024

A complex instruction set computer (CISC /ˈsɪsk/) is a computer architecture in which single instructions can execute several low-level operations (such...

16 KB (2,109 words) - 22:17, 28 June 2025

scientist noted for his work on VLIW architectures, compiling, and instruction-level parallelism, and for the founding of Multiflow Computer. He is a Hewlett-Packard...

8 KB (783 words) - 01:08, 30 June 2025

instruction is fetched every clock cycle by exploiting instruction-level parallelism, therefore, since one could theoretically have five instructions...

6 KB (914 words) - 12:02, 29 July 2025

Program counter (redirect from Instruction pointer)

concept of "where it is in its sequence" is too simplistic, as instruction-level parallelism and out-of-order execution may occur. In a processor where the...

12 KB (1,382 words) - 23:43, 21 June 2025

Loop-level parallelism is a form of parallelism in software programming that is concerned with extracting parallel tasks from loops. The opportunity for...

15 KB (2,046 words) - 00:27, 2 May 2024

Simultaneous multithreading (redirect from Chip-level multithreading)

increase on-chip parallelism with fewer resource requirements: one is superscalar technique which tries to exploit instruction-level parallelism (ILP); the...

22 KB (2,467 words) - 05:57, 6 August 2025

to be parallelized by the processor by taking advantage of instruction-level parallelism. This is possible when there are no data dependencies between...

9 KB (1,149 words) - 04:07, 21 July 2025

MIPS architecture (redirect from MIPS instruction set)

addressing modes). MIPS IV added several features to improve instruction-level parallelism. To alleviate the bottleneck caused by a single condition bit...

70 KB (8,083 words) - 19:26, 27 July 2025

interaction (task parallelism). These forms of parallelism are accommodated by various hardware strategies, including instruction-level parallelism (such as instruction...

38 KB (4,448 words) - 08:48, 14 July 2025

Task parallelism (also known as function parallelism and control parallelism) is a form of parallelization of computer code across multiple processors...

6 KB (769 words) - 23:31, 31 July 2024

to: Inductive logic programming Information Leak Prevention Instruction-level parallelism Integer linear programming ilp., a 2013 album by Kwes Independent...

996 bytes (154 words) - 17:43, 24 December 2024

disadvantage of a MISC is that instructions tend to have more sequential dependencies, reducing overall instruction-level parallelism. MISC architectures have...

12 KB (1,412 words) - 10:29, 27 May 2025

purpose 64-bit CPU with a superscalar core. It supports internal instruction-level parallelism, and includes simultaneous multithreading (SMT). It doesn't...

25 KB (2,755 words) - 00:59, 26 May 2025

Multithreading (computer architecture) (category Instruction processing)

paradigm has become more popular as efforts to further exploit instruction-level parallelism have stalled since the late 1990s. This allowed the concept...

13 KB (1,559 words) - 20:42, 14 April 2025

of these false data dependencies reveals more instruction-level parallelism in an instruction stream, which can be exploited by various and complementary...

29 KB (4,262 words) - 02:21, 16 February 2025