computing, interrupt latency refers to the delay between the start of an Interrupt Request (IRQ) and the start of the respective Interrupt Service Routine...

6 KB (667 words) - 15:33, 21 August 2024

Microcontroller (section Interrupt latency)

systems often seek to optimize interrupt latency over instruction throughput. Issues include both reducing the latency, and making it be more predictable...

44 KB (5,266 words) - 19:38, 23 June 2025

Inter-processor interrupt (IPI) Interrupt Interrupt handler Interrupt latency Message Signaled Interrupts (MSI) Non-maskable interrupt (NMI) Intel MultiProcessor...

17 KB (2,024 words) - 14:59, 15 June 2025

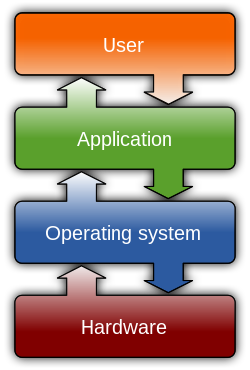

applications. Key factors in a real-time OS are minimal interrupt latency and minimal thread switching latency; a real-time OS is valued more for how quickly or...

16 KB (2,275 words) - 03:27, 20 June 2025

from Intel OpenPIC and IBM MPIC Inter-processor interrupt (IPI) Interrupt latency Non-maskable interrupt (NMI) IRQL (Windows) "Intel® 64 and IA-32 Architectures...

4 KB (424 words) - 17:15, 6 April 2025

supported up to 224 MSI-based interrupts. According to a 2009 Intel benchmark using Linux, using MSI reduced the latency of interrupts by a factor of almost three...

13 KB (1,535 words) - 16:49, 7 May 2024

Context switch (redirect from Thread switching latency)

latency. The time to switch between two threads of the same process is called the thread switching latency. The time from when a hardware interrupt is...

15 KB (1,963 words) - 07:06, 23 February 2025

Interrupts". Coleman, James (2009). "Results, Workstation Class Platform". Reducing Interrupt Latency Through the Use of Message Signalled Interrupts...

10 KB (1,273 words) - 12:33, 27 December 2024

experience some sort of latency, regardless of the nature of the stimulation to which it has been exposed. The precise definition of latency depends on the system...

17 KB (2,213 words) - 12:31, 13 May 2025

needed] Interrupt vector table Advanced Programmable Interrupt Controller (APIC) Inter-processor interrupt (IPI) Interrupt latency Interrupts in 65xx...

13 KB (1,799 words) - 05:59, 15 April 2025

(TCM): Low-latency (zero wait state) SRAM that can be used to hold the call stack, RTOS control structures, interrupt data structures, interrupt handler...

82 KB (5,916 words) - 05:29, 6 August 2025

interrupt (IPI) Interrupt Interrupt handler Interrupt latency Programmable Interrupt Controller (PIC) "Interrupt Levels". Retrieved 2023-11-30. "8.7.2: MS-DOS*...

8 KB (995 words) - 08:46, 14 June 2025

the interrupt. This increases the maximum bit rate the computer can process reliably from 9600 to 153,000 bit/s if it has a 1 millisecond interrupt dead...

38 KB (3,036 words) - 18:43, 25 July 2025

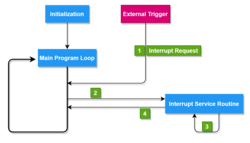

In digital computers, an interrupt is a request for the processor to interrupt currently executing code (when permitted), so that the event can be processed...

46 KB (5,726 words) - 14:31, 9 July 2025

helps reduce interrupt latency as the interrupt service routine can be executed directly without determining the source of the interrupt. A context save...

2 KB (221 words) - 20:02, 24 August 2024

processor usually makes latency worse, but makes throughput better. Computers that control machinery usually need low interrupt latencies. These computers operate...

27 KB (3,259 words) - 02:35, 27 July 2025

Intel 8259 (category Interrupts)

1986 Advanced Programmable Interrupt Controller (APIC) IF (x86 flag) Interrupt handler Interrupt latency Non-maskable interrupt (NMI) "Intel datasheet"....

11 KB (1,618 words) - 12:17, 6 July 2025

that re-enables interrupts early in the interrupt handler. This may reduce interrupt latency. In general, while programming interrupt service routines...

18 KB (2,043 words) - 14:01, 1 July 2025

guarantee worst-case response. That is easier to do when the CPU has low interrupt latency and when it has deterministic response. (DSP) Computer programmers...

21 KB (2,416 words) - 05:53, 6 August 2025

to have bounded (and preferably short) running time, or excessive interrupt latency may be observed. A lock-free data structure can be used to improve...

19 KB (2,392 words) - 03:11, 22 June 2025

Computer performance (section Latency)

input distribution. Latency is a time delay between the cause and the effect of some physical change in the system being observed. Latency is a result of the...

22 KB (2,841 words) - 23:36, 9 March 2025

resume execution at the instruction immediately following WAI. Hence interrupt latency will be very short (70 nanoseconds at 14 megahertz), resulting in...

29 KB (3,677 words) - 13:05, 21 December 2024

technique can reduce interrupt load by up to an order of magnitude, while only incurring relatively small latency penalties. Interrupt coalescing is typically...

2 KB (196 words) - 05:51, 23 August 2024

instruction cycle jitter. Internal interrupts are already synchronized. The constant interrupt latency allows PICs to achieve interrupt-driven low-jitter timing...

68 KB (8,414 words) - 18:39, 18 July 2025

expensive monitors or monitors that have a higher resolution. Latency (engineering) Interrupt latency Application Response Measurement Wescott, Bob (2013). The...

5 KB (720 words) - 07:28, 3 June 2024

Programmable Interrupt Controller (APIC) OpenPIC and IBM MPIC Inter-processor interrupt (IPI) Interrupt latency Non-maskable interrupt (NMI) IRQL (Windows)...

2 KB (239 words) - 08:44, 27 March 2023

Compared to these the programmable interrupt controller of the Intel CPUs (8086..80586) generates a very large latency and the Windows operating system...

26 KB (3,408 words) - 05:58, 18 July 2025

extension) has been developed to extend the interrupt controller support, reduce the interrupt latency and enhance the I/O peripheral control function...

70 KB (8,083 words) - 19:26, 27 July 2025

processed. WAit-for-Interrupt (WAI) and SToP (STP, stop-the-clock) instructions reduce power consumption, decrease interrupt latency and enable synchronization...

37 KB (4,396 words) - 08:22, 30 July 2025

context switching, network, application startup time, load, frame loss, interrupt latency, etc., and also performance optimised in smart routers and smart vehicles...

47 KB (3,784 words) - 05:37, 6 August 2025