in a table of interrupt vectors. Each entry of the interrupt vector table, called an interrupt vector, is the address of an interrupt handler (also known...

5 KB (492 words) - 01:28, 4 November 2024

The interrupt descriptor table (IDT) is a data structure used by the x86 architecture to implement an interrupt vector table. The IDT is used by the processor...

8 KB (1,201 words) - 01:51, 20 May 2025

usually dispatched via a hard-coded table of interrupt vectors, asynchronously to the normal execution stream (as interrupt masking levels permit), often using...

13 KB (1,799 words) - 05:59, 15 April 2025

looking it up in a table of ISR starting-point addresses (called "interrupt vectors") in memory: the Interrupt vector table (IVT). An interrupt is invoked by...

29 KB (3,319 words) - 17:50, 25 July 2024

INT (x86 instruction) (redirect from Interrupt 3)

while in real mode (see interrupt vector). It is therefore entirely possible to use a far-call instruction to start the interrupt-function manually after...

4 KB (472 words) - 17:32, 29 November 2024

distinct interrupt routine for each type of interrupt (or for each interrupt source), often implemented as one or more interrupt vector tables. To mask...

43 KB (5,520 words) - 20:23, 23 May 2025

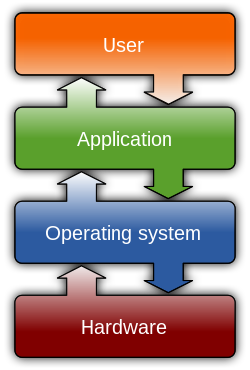

Operating system (section Software interrupt)

placed in a system table.) Read the integer from the data bus. The integer is an offset to the interrupt vector table. The vector table's instructions will...

70 KB (8,176 words) - 14:39, 31 May 2025

BIOS (redirect from Software licensing description table)

below address 0x00400 contains the interrupt vector table. BIOS POST has initialized the system timers, interrupt controller(s), DMA controller(s), and...

89 KB (9,559 words) - 19:02, 5 May 2025

Motorola 68000 (section Interrupts)

"exception table" (interrupt vector table interrupt vector addresses) is fixed at addresses 0 through 1023, permitting 256 32-bit vectors. The first vector (RESET)...

69 KB (7,389 words) - 14:24, 25 May 2025

Zero page (section Interrupt vectors)

space for the interrupt vector table (IVT) if they run in real mode. A similar technique of using the zero page for hardware related vectors was employed...

12 KB (1,404 words) - 00:01, 27 December 2024

starting at address 0, is the permanent, immovable location of the interrupt vector table.) So, the actual amount of memory addressable by the 80286 and later...

10 KB (1,508 words) - 10:08, 25 June 2024

identically to an interrupt: the processor halts execution of the current program, looks up the interrupt handler in the interrupt vector table for that exception...

17 KB (1,806 words) - 04:12, 1 December 2023

bytes of the interrupt service routine entry point reserved for INT 30h and the first byte of INT 31h in the x86 real mode interrupt vector table). However...

42 KB (4,913 words) - 02:36, 21 May 2025

reset. The reset vector for 68000 processor family is 0x00000000 for Initial Interrupt Stack Register (IISR; Not really a reset vector and is used to initialize...

9 KB (1,028 words) - 19:02, 4 September 2024

that had previously altered the same interrupt vector. Cascade with other TSRs by calling the old interrupt vector. This can be done before or after they...

13 KB (1,799 words) - 03:07, 6 June 2025

is booted from an infected sector, Form goes resident, hooks the interrupt vector table, and runs the original boot sector which it has hidden in an area...

5 KB (594 words) - 01:31, 8 March 2025

IVT may refer to: Interrupt vector table, a memory construct in some processors Intel Virtualization Technology, a computer processor feature to simplify...

945 bytes (129 words) - 17:21, 3 July 2023

The interrupt disable flag is set in the status register. 65C816/65C802: PB is loaded with $00. PC is loaded from the relevant vector (see tables). The...

29 KB (3,677 words) - 13:05, 21 December 2024

SENDUIPI is an index to pick an entry from the UITT (User-Interrupt Target Table, a table specified by the new UINTR_TT and UINT_MISC MSRs.) On Sapphire...

263 KB (14,911 words) - 15:01, 7 May 2025

section that starts up the modules. Other well-known examples are the interrupt vector table and the main loop. Some functions inherently have mixed semantics...

4 KB (476 words) - 01:00, 21 November 2024

Hooking (section Virtual method table hooking)

on systems using the shared library concept, the interrupt vector table or the import descriptor table can be modified in memory. Essentially these tactics...

25 KB (2,983 words) - 03:57, 4 April 2025

between LAPICs. A single LAPIC may support up to 224 usable interrupt vectors from an I/O APIC. Vector numbers 0 to 31, out of 0 to 255, are reserved for exception...

17 KB (2,024 words) - 14:59, 15 June 2025

Task state segment (redirect from Interrupt Stack Table)

the Interrupt Stack Table (IST), which also resides in the TSS and contains logical (segment+offset) stack pointers. If an interrupt descriptor table specifies...

10 KB (1,543 words) - 13:46, 26 February 2025

equivalent to the BIOS in modern PCs. ROM #0 also contains the interrupt vector table at FFF0-FFFF. FFFE-FFFF determines what the program counter should...

17 KB (1,553 words) - 11:08, 10 April 2025

INT 13H (redirect from Interrupt 13h)

interrupt call 13hex, the 20th interrupt vector in an x86-based (IBM PC-descended) computer system. The BIOS typically sets up a real mode interrupt handler...

30 KB (1,945 words) - 15:08, 17 March 2025

in instruction fetch cycles if the programmer has configured the interrupt vector table to fall within the contended area. In that case the ULA will decline...

4 KB (558 words) - 19:09, 1 December 2024

WD16 (section Interrupts)

a four-bit interrupt number provided by the interrupting device. The interrupt vector table address is fetched from 0028 and the interrupt number is added...

51 KB (3,487 words) - 21:49, 6 May 2025

AArch64 (redirect from Scalable vector extension)

128-bit translation tables (ARMv9 only). Scalable Matrix Extension 2 (SME2) (ARMv9 only). Multi-vector instructions. Multi-vector predicates. 2b/4b weight...

40 KB (3,505 words) - 10:26, 11 June 2025

addressing modes, including zero page addressing. Vector pull (VPB) output indicates when interrupt vectors are being addressed. Memory lock (MLB) output...

37 KB (4,396 words) - 15:24, 29 May 2025

first 128 KB of the address space. The first bank overlaps the interrupt vector table of the x86 CPU and the data area used by the BIOS, so it is generally...

19 KB (2,110 words) - 10:31, 27 May 2025