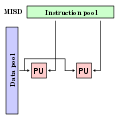

In computing, multiple instruction, single data (MISD) is a type of parallel computing architecture where many functional units perform different operations...

6 KB (759 words) - 19:38, 10 July 2025

Single instruction, multiple data (SIMD) is a type of parallel computing (processing) in Flynn's taxonomy. SIMD describes computers with multiple processing...

36 KB (4,365 words) - 18:33, 30 July 2025

In computing, multiple instruction, multiple data (MIMD) is a technique employed to achieve parallelism. Machines using MIMD have a number of processor...

8 KB (969 words) - 13:12, 19 July 2025

Single instruction, multiple threads (SIMT) is an execution model used in parallel computing where a single central "Control Unit" broadcasts an instruction...

12 KB (1,289 words) - 20:20, 1 August 2025

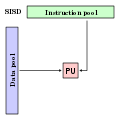

single instruction stream, single data stream (SISD) is a computer architecture in which a single uni-core processor executes a single instruction stream...

2 KB (204 words) - 12:17, 1 June 2025

computing, single program, multiple data (SPMD) is a term that has been used to refer to computational models for exploiting parallelism whereby multiple processors...

16 KB (2,071 words) - 17:14, 26 July 2025

based on spatial designs. They are sometimes classified as multiple-instruction single-data (MISD) architectures under Flynn's taxonomy, but this classification...

19 KB (2,543 words) - 16:46, 1 August 2025

four instructions. 3-operand, allowing better reuse of data: CISC — It becomes either a single instruction: add a,b,c C = A+B needs one instruction. CISC...

35 KB (4,329 words) - 19:12, 27 June 2025

Multiprocessing (redirect from Multiple processing units)

execute a single sequence of instructions in multiple contexts (single instruction, multiple data or SIMD, often used in vector processing), multiple sequences...

13 KB (1,557 words) - 08:35, 24 April 2025

PCs had multiple cores) and mainframe computers. A single instruction is simultaneously applied to multiple different data streams. Instructions can be...

15 KB (1,722 words) - 02:10, 4 August 2025

(computing), aka a data pipeline, a set of data processing elements connected in series Protocol pipelining, a technique in which multiple requests are written...

759 bytes (126 words) - 13:25, 10 November 2023

SIGGRAPH—Special Interest Group on Graphics SIMD—Single Instruction, Multiple Data SIM—Subscriber Identity Module SIMM—Single Inline Memory Module SIP—Session Initiation...

118 KB (8,321 words) - 02:28, 4 August 2025

Parallel computing (redirect from Multiple processing elements)

The single-instruction-single-data (SISD) classification is equivalent to an entirely sequential program. The single-instruction-multiple-data (SIMD) classification...

74 KB (8,380 words) - 19:27, 4 June 2025

Superscalar processor (redirect from Multiple issue)

processor (or multiple-issue processor) is a CPU that implements a form of parallelism called instruction-level parallelism within a single processor. In...

14 KB (1,678 words) - 19:56, 4 June 2025

MMX is a single instruction, multiple data (SIMD) instruction set architecture designed by Intel, introduced on January 8, 1997 with its Pentium P5 (microarchitecture)...

15 KB (1,452 words) - 07:01, 28 January 2025

The x86 instruction set has several times been extended with SIMD (Single instruction, multiple data) instruction set extensions. These extensions, starting...

155 KB (6,191 words) - 19:46, 20 July 2025

Vector processor (section Vector instruction example)

whose instructions operate on single data items only, and in contrast to some of those same scalar processors having additional single instruction, multiple...

68 KB (9,534 words) - 21:55, 3 August 2025

School District (Iowa) Macomb Intermediate School District Multiple instruction, single data, a parallel computing architecture Misdemeanor, a criminal...

379 bytes (73 words) - 17:18, 6 June 2024

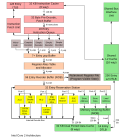

CPU cache (redirect from Instruction cache)

have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with separate instruction-specific (I-cache) and data-specific (D-cache)...

99 KB (13,735 words) - 12:24, 8 July 2025

Multithreading (computer architecture) (category Instruction processing)

ability of a central processing unit (CPU) (or a single core in a multi-core processor) to provide multiple threads of execution. The multithreading paradigm...

13 KB (1,559 words) - 20:42, 14 April 2025

instruction includes the address of the data. One-address machines have the disadvantage that even simple actions like an addition require multiple instructions...

21 KB (3,017 words) - 05:34, 20 April 2025

average number of instructions run per step of this parallel execution.: 5 ILP must not be confused with concurrency. In ILP, there is a single specific thread...

9 KB (1,026 words) - 00:26, 27 January 2025

processor chip design company Single instruction, multiple data – Type of parallel processing Single instruction, multiple threads – Execution model used...

24 KB (3,038 words) - 22:21, 26 January 2025

Scalar processor (redirect from Scalar data types)

processor where a single instruction operates simultaneously on multiple data items (and thus is referred to as a single instruction, multiple data (SIMD) processor)...

3 KB (318 words) - 16:19, 26 April 2025

Streaming SIMD Extensions (redirect from Katmai New Instructions)

computing, Streaming SIMD Extensions (SSE) is a single instruction, multiple data (SIMD) instruction set extension to the x86 architecture, designed by...

14 KB (1,543 words) - 17:34, 9 June 2025

instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the base x86 instruction set...

17 KB (1,747 words) - 00:59, 3 June 2025

Word (computer architecture) (redirect from Data word)

any processor design's natural unit of data. A word is a fixed-sized datum handled as a unit by the instruction set or the hardware of the processor. The...

41 KB (3,657 words) - 01:15, 3 May 2025

Microarchitecture (category Instruction processing)

programs, all single- or multi-chip CPUs: Read an instruction and decode it Find any associated data that is needed to process the instruction Process the...

27 KB (3,576 words) - 23:42, 21 June 2025

feature-reduced single-chip implementation of the POWER1, a multi-chip central processing unit (CPU) which implemented the POWER instruction set architecture...

4 KB (655 words) - 23:51, 19 February 2023

the instructions are available in real mode as well. The descriptors used by the LGDT, LIDT, SGDT and SIDT instructions consist of a 2-part data structure...

265 KB (15,000 words) - 22:03, 26 July 2025