very different. Many instruction set architectures have instructions that, on some implementations of that instruction set architecture, operate on half and/or...

34 KB (1,883 words) - 05:32, 6 August 2025

multiply–accumulate multiplier. Comparison of instruction set architectures Compressed instruction set Computer architecture Emulator Instruction set simulator Micro-operation...

35 KB (4,329 words) - 19:12, 27 June 2025

instructions.[citation needed] Specific instruction set architectures that have been retroactively labeled CISC are System/360 through z/Architecture...

16 KB (2,109 words) - 22:17, 28 June 2025

Machines and originally Acorn RISC Machine) is a family of RISC instruction set architectures (ISAs) for computer processors. Arm Holdings develops the...

145 KB (13,891 words) - 11:31, 6 August 2025

Central processing unit (redirect from Instruction decoder)

processor Graphics processing unit Comparison of instruction set architectures Protection ring Reduced instruction set computer Stream processing True Performance...

101 KB (11,434 words) - 05:49, 18 July 2025

Comparison of CPUs may refer to: Comparison of CPU microarchitectures Comparison of instruction set architectures List of AMD microprocessors List of...

231 bytes (56 words) - 00:14, 20 June 2019

LWP instructions developed specifically for the "Bulldozer" family of micro-architectures. These are integer version of the FMA instruction set. These...

20 KB (1,448 words) - 04:33, 31 August 2024

a reduced instruction set computer (RISC) (pronounced "risk") is a computer architecture designed to simplify the individual instructions given to the...

62 KB (7,270 words) - 23:22, 6 July 2025

The x86 instruction set refers to the set of instructions that x86-compatible microprocessors support. The instructions are usually part of an executable...

265 KB (15,000 words) - 06:03, 6 August 2025

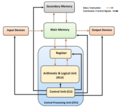

the instruction set architecture design, microarchitecture design, logic design, and implementation. The first documented computer architecture was in...

27 KB (3,259 words) - 02:35, 27 July 2025

instruction set includes the set of valid operations for the Burroughs B6500, B7500 and later Burroughs large systems, including the current (as of 2006)...

29 KB (4,040 words) - 08:21, 8 May 2023

Interlocked Pipelined Stages) is a family of reduced instruction set computer (RISC) instruction set architectures (ISA): A-1 : 19 developed by MIPS Computer...

70 KB (8,083 words) - 19:26, 27 July 2025

In computer engineering, an orthogonal instruction set is an instruction set architecture where all instruction types can use all addressing modes. It...

21 KB (3,017 words) - 05:34, 20 April 2025

Machine code (redirect from Jump into the middle of instruction)

the VAX architecture, which includes optional support of the PDP-11 instruction set; the IA-64 architecture, which includes optional support of the IA-32...

38 KB (3,880 words) - 10:47, 24 July 2025

An Advanced Encryption Standard instruction set (AES instruction set) is a set of instructions that are specifically designed to perform AES encryption...

26 KB (2,239 words) - 05:25, 6 August 2025

supported by a complete suite of development tools. List of common microcontrollers Comparison of instruction set architectures "Overcoming the power/performance...

8 KB (721 words) - 15:52, 7 July 2025

The following is a comparison of CPU microarchitectures. Processor design Comparison of instruction set architectures According to AMDs K5 data sheet....

18 KB (175 words) - 01:12, 20 July 2025

SIMD can be internal (part of the hardware design) and it can be directly accessible through an instruction set architecture (ISA), but it should not be...

36 KB (4,352 words) - 10:43, 4 August 2025

An instruction set simulator (ISS) is a simulation model, usually coded in a high-level programming language, which mimics the behavior of a mainframe...

14 KB (1,891 words) - 02:56, 24 June 2024

Processor design (redirect from CPU Architecture)

Amdahl's law Central processing unit Comparison of instruction set architectures Complex instruction set computer CPU cache Electronic design automation...

21 KB (2,416 words) - 05:53, 6 August 2025

Microprocessor (redirect from History of the microprocessor)

year are embedded. Comparison of instruction set architectures Computer architecture Computer engineering Heterogeneous computing List of microprocessors...

82 KB (9,697 words) - 01:31, 23 July 2025

processor types. GNU Assembler (GAS): GPL: many target instruction sets, including ARM architecture, Atmel AVR, x86, x86-64, RISC-V, Freescale 68HC11, Freescale...

23 KB (505 words) - 11:50, 13 June 2025

AVX-512 (redirect from Vector Neural Network Instructions)

extensions to the 256-bit Advanced Vector Extensions SIMD instructions for x86 instruction set architecture (ISA) proposed by Intel in July 2013, and first implemented...

86 KB (4,691 words) - 05:30, 6 August 2025

RISC-V assembly language (section Instruction types)

code for the RISC-V class of processors. Assembly languages are closely tied to the architecture's machine code instructions, allowing for precise control...

4 KB (306 words) - 20:40, 13 March 2025

The x86 instruction set has several times been extended with SIMD (Single instruction, multiple data) instruction set extensions. These extensions, starting...

155 KB (6,191 words) - 19:46, 20 July 2025

X86 assembly language (category X86 architecture)

syntax is nearly universal across other architectures (retaining the same operand order for the mov instruction); it was originally designed for PDP-11...

57 KB (6,649 words) - 00:22, 6 August 2025

The Harvard architecture is a computer architecture with separate storage and signal pathways for instructions and data. It is often contrasted with the...

14 KB (1,852 words) - 04:51, 18 July 2025

The Atmel AVR instruction set is the machine language for the Atmel AVR, a modified Harvard architecture 8-bit RISC single chip microcontroller which was...

42 KB (2,722 words) - 08:58, 17 May 2025

Advanced Vector Extensions (redirect from Haswell New Instructions)

Sandy Bridge New Instructions) are SIMD extensions to the x86 instruction set architecture for microprocessors from Intel and Advanced Micro Devices (AMD)...

52 KB (4,113 words) - 05:25, 6 August 2025

ARM Cortex-M (redirect from ARMv6-M architecture)

Only Thumb-1 and Thumb-2 instruction sets are supported in Cortex-M architectures; the legacy 32-bit ARM instruction set isn't supported. All Cortex-M...

82 KB (5,916 words) - 05:29, 6 August 2025