version of AES-NI, AVX-512 Vector AES instructions (VAES), is found in AVX-512. The following Intel processors support the AES-NI instruction set: Westmere...

26 KB (2,215 words) - 14:42, 13 April 2025

CLMUL instruction set can be checked by testing one of the CPU feature bits. Finite field arithmetic AES instruction set FMA3 instruction set FMA4 instruction...

6 KB (492 words) - 03:05, 13 May 2025

processor's instruction set. For example, the AES encryption algorithm (a modern cipher) can be implemented using the AES instruction set on the ubiquitous...

15 KB (1,251 words) - 08:41, 27 May 2025

Intel AES instruction set) and on SPARC (using the SPARC AES instruction set). It is available in Solaris and derivatives, as of Solaris 10. OpenAES portable...

12 KB (1,295 words) - 16:41, 13 July 2025

standardization as AES AES instruction set, an x86 microprocessor architecture addition improving Advanced Encryption Standard implementation AES may also refer...

4 KB (474 words) - 07:12, 20 January 2025

Advanced Vector Extensions (AVX) AES instruction set CLMUL instruction set F16C FMA instruction set Intel ADX XOP instruction set Intel BCD opcodes (also used...

19 KB (1,446 words) - 21:46, 26 July 2025

acceleration of the Rijndael algorithm via the AES instruction set; Rijndael implementations that use the instruction set are now orders of magnitude faster than...

9 KB (827 words) - 14:21, 3 April 2025

VIA PadLock (category Instruction processing)

OpenSSL supports PadLock AES and SHA since 2004 (0.9.7f/0.9.8a). GNU assembler supports PadLock since 2004. AES instruction set Block cipher mode of operation...

4 KB (391 words) - 10:02, 17 July 2025

STU-III VINSON Other JADE KG-84 KL-43 KL-51 Noreen Red Purple Pinwheel Rockex Computer hardware AES instruction set Intel SHA extensions IBM 4758 IBM 4764...

7 KB (920 words) - 14:16, 11 May 2025

The FMA instruction set is an extension to the 128- and 256-bit Streaming SIMD Extensions instructions in the x86 microprocessor instruction set to perform...

19 KB (1,395 words) - 13:44, 19 July 2025

STU-III VINSON Other JADE KG-84 KL-43 KL-51 Noreen Red Purple Pinwheel Rockex Computer hardware AES instruction set Intel SHA extensions IBM 4758 IBM 4764...

12 KB (1,687 words) - 00:30, 11 November 2024

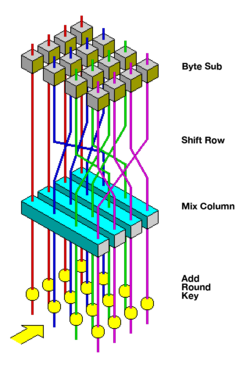

Advanced Encryption Standard (redirect from AES-256)

CPUs supporting AES-NI instruction set extensions, throughput can be multiple GiB/s. On an Intel Westmere CPU, AES encryption using AES-NI takes about...

50 KB (5,679 words) - 04:23, 27 July 2025

Minimal instruction set computer (MISC) is a central processing unit (CPU) architecture, usually in the form of a microprocessor, with a very small number...

12 KB (1,412 words) - 10:29, 27 May 2025

RDRAND (redirect from Bull Mountain (instruction))

disabling the additional security checks for instructions executing outside of an SGX enclave. AES instruction set Bullrun (decryption program) wolfSSL In...

26 KB (2,638 words) - 21:55, 9 July 2025

Operations) instruction set, announced by AMD on May 1, 2009, is an extension to the 128-bit SSE core instructions in the x86 and AMD64 instruction set for the...

20 KB (1,448 words) - 04:33, 31 August 2024

The x86 instruction set refers to the set of instructions that x86-compatible microprocessors support. The instructions are usually part of an executable...

265 KB (15,000 words) - 22:03, 26 July 2025

AES encryption expose this to programs through an extension of the instruction set architecture (ISA) of the various chipsets (e.g. AES instruction set...

6 KB (494 words) - 03:34, 24 December 2024

InvShiftRows/InvSubBytes steps of an AES decryption round. For the intended AES decode flow under AES-NI (a series of AESDEC instructions followed by an AESDECLAST)...

36 KB (1,802 words) - 22:08, 8 June 2025

purposes, including for storing cryptographic data when using the AES instruction set, present in many Intel CPUs. This means that this vulnerability may...

7 KB (828 words) - 21:56, 9 July 2025

seven new instructions (AES instruction set or AES-NI), out of which six implement the AES algorithm, and PCLMULQDQ (see CLMUL instruction set) implements...

22 KB (530 words) - 06:42, 6 July 2025

attacks by design of the AES-NI instruction, where the CPU supports AES instruction set extensions. Processors capable of handling AES extensions as of 2011...

10 KB (1,300 words) - 20:28, 28 December 2022

Authenticated encryption (redirect from AE scheme)

messages to exist can be used. AEGIS is an example of fast (if the AES instruction set is present), key-committing AEAD. It is possible to add key-commitment...

19 KB (2,087 words) - 13:23, 24 July 2025

CPUs support Advanced Encryption Standard (AES) encoding and decoding in hardware, using the AES instruction set proposed by Intel in March 2008. Allwinner...

4 KB (392 words) - 10:06, 18 July 2025

Encryption Standard (AES) algorithm on systems where the CPU does not feature AES acceleration (such as the AES instruction set for x86 processors). As...

32 KB (3,624 words) - 17:22, 25 June 2025

STU-III VINSON Other JADE KG-84 KL-43 KL-51 Noreen Red Purple Pinwheel Rockex Computer hardware AES instruction set Intel SHA extensions IBM 4758 IBM 4764...

823 bytes (82 words) - 14:45, 4 December 2017

chosen from a set of five. In 1938, the Navy added two more rotors, and then another in 1939 to allow a choice of three rotors from a set of eight. A four-rotor...

94 KB (11,505 words) - 08:05, 23 July 2025

series of cams (or "pins") around their circumference. These cams could be set in a raised (active) or lowered (inactive) position. In the raised position...

34 KB (3,793 words) - 06:34, 25 May 2025

Masters — shift-leader Max Newman — mathematician and codebreaker who later set up the Newmanry Denis Oswald — linguist and senior codebreaker Jerry Roberts...

14 KB (1,477 words) - 20:11, 16 April 2025

AVX-512 (redirect from Vector Neural Network Instructions)

extensions to the 256-bit Advanced Vector Extensions SIMD instructions for x86 instruction set architecture (ISA) proposed by Intel in July 2013, and first...

85 KB (4,667 words) - 21:58, 16 July 2025

STU-III VINSON Other JADE KG-84 KL-43 KL-51 Noreen Red Purple Pinwheel Rockex Computer hardware AES instruction set Intel SHA extensions IBM 4758 IBM 4764...

2 KB (265 words) - 03:49, 9 May 2025