In digital electronics, an address decoder is a binary decoder that has two or more inputs for address bits and one or more outputs for device selection...

4 KB (527 words) - 10:01, 11 June 2023

Memory-mapped I/O and port-mapped I/O (redirect from Complete address decoder)

interface). Address decoding types, in which a device may decode addresses completely or incompletely, include the following: Complete (exhaustive) decoding 1:1...

17 KB (2,288 words) - 01:44, 18 November 2024

register). The sum-addressed decoder is going to decode R+O. For each decoder line, call the line number L. Suppose that our decoder drove both R and O...

13 KB (2,076 words) - 21:31, 12 April 2023

output of a ring counter) Priority encoder Sum-addressed decoder US patent 5313300A, "Binary to unary decoder for a video digital to analog converter", issued...

4 KB (637 words) - 02:43, 25 February 2025

Simple Bus Architecture (section Address decoder)

execute next). This addressing communicates directly with the Address Decoder. Assigns each slave core a position in the address map and enables these...

7 KB (811 words) - 02:49, 26 December 2024

n-bit word (e.g. N= 2100 100-bit words), and let the address decoding be done by N address decoder neurons. Set the threshold of each neuron x to its maximum...

56 KB (7,736 words) - 09:08, 27 May 2025

Märklin Digital (redirect from Märklin decoders)

be fitted with a decoder circuit which will interpret instructions and individually control the motor. Each decoder has its own address, instructions sent...

27 KB (3,828 words) - 03:09, 17 June 2025

CPU cache (redirect from Virtual-to-physical address translation)

few gate delays by collapsing the virtual address adder into the SRAM decoders. See sum-addressed decoder. The early history of cache technology is closely...

97 KB (13,324 words) - 06:26, 27 May 2025

Translation lookaside buffer (redirect from Address Translation Registers)

memory address to a physical memory location. It is used to reduce the time taken to access a user memory location. It can be called an address-translation...

25 KB (3,339 words) - 23:39, 2 June 2025

immediately and not pipelined. With forwarding enabled, the Instruction Decode/Execution (ID/EX) stage of the pipeline now has two inputs: the value read...

10 KB (1,237 words) - 10:14, 13 February 2025

Transformer (deep learning architecture) (redirect from Encoder–decoder model)

final_layer_norm(z_e[t]) /* decoder */ z_d ← decoder.tokenizer(t_d) for each t in 1:length(z_d) do z_d[t] ← decoder.embedding(z_d[t]) + decoder.positional_embedding(t)...

106 KB (13,107 words) - 01:06, 16 June 2025

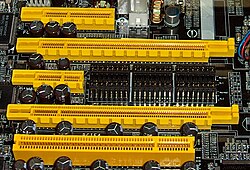

Bus (computing) (redirect from Address bus)

portal Address decoder Bus contention Bus error Bus mastering Communication endpoint Computer port (hardware) Control bus Crossbar switch Memory address Front-side...

31 KB (3,941 words) - 11:43, 23 May 2025

URL (redirect from Web address)

A uniform resource locator (URL), colloquially known as an address on the Web, is a reference to a resource that specifies its location on a computer...

17 KB (2,359 words) - 11:36, 28 May 2025

Multiplexer Demultiplexer Adder Multiplier CPU Binary decoder Address decoder Sum-addressed decoder Barrel shifter Circuitry Integrated circuit 3D Mixed-signal...

22 KB (2,135 words) - 18:53, 16 May 2025

used in other parts of the processor, where they are used to calculate addresses, table indices, increment and decrement operators and similar operations...

24 KB (2,891 words) - 19:38, 6 June 2025

biological ALUs has been carried out (e.g., actin-based). Adder (electronics) Address generation unit (AGU) Binary multiplier Execution unit Load–store unit...

27 KB (3,326 words) - 15:57, 30 May 2025

machine. When using binary, a decoder is needed to determine the state. A one-hot state machine, however, does not need a decoder as the state machine is in...

9 KB (1,194 words) - 07:11, 25 May 2025

Multiplexer Demultiplexer Adder Multiplier CPU Binary decoder Address decoder Sum-addressed decoder Barrel shifter Circuitry Integrated circuit 3D Mixed-signal...

8 KB (1,031 words) - 20:28, 28 February 2025

during testing such as: Stuck-at Faults (SAFs) Transition Faults (TFs) Address Decoder Faults (AFs) Coupling Faults (CFs), such as Inversion (CFin), Idempotent...

3 KB (347 words) - 19:12, 27 May 2025

Multiplexer Demultiplexer Adder Multiplier CPU Binary decoder Address decoder Sum-addressed decoder Barrel shifter Circuitry Integrated circuit 3D Mixed-signal...

11 KB (1,739 words) - 05:02, 2 November 2024

contains a copy of the value in the memory location specified by the memory address register. It acts as a buffer, allowing the processor and memory units...

3 KB (354 words) - 04:11, 26 May 2025

Multiplexer Demultiplexer Adder Multiplier CPU Binary decoder Address decoder Sum-addressed decoder Barrel shifter Circuitry Integrated circuit 3D Mixed-signal...

13 KB (1,583 words) - 11:59, 23 May 2025

systems, the memory address register always drives the address bus, the control unit always drives the control bus, and an address decoder selects which particular...

13 KB (1,648 words) - 08:39, 27 May 2025

UART (serial controller interface) channels Internal configurable address decoder Three PIA (Programmable I/O adapter) ports Two 16-bit timers One CSIO...

2 KB (239 words) - 17:10, 16 June 2024

all resources to all slots, and each peripheral device had its own address decoding for the registers or memory blocks it needed to communicate with the...

19 KB (2,228 words) - 11:41, 8 April 2025

Random-access memory (section Addressing)

random-access memory was often constructed using diode matrices driven by address decoders, or specially wound core rope memory planes.[citation needed] Semiconductor...

58 KB (5,812 words) - 21:59, 11 June 2025

microprocessor U2 = 74HC373P address latch U3 = CD4060BCN 14-bit asynchronous binary counter U4 = 74HC139N address decoder U5 = Static RAM (130 kB) U6...

4 KB (522 words) - 16:12, 29 August 2024

was possible to add more memory to the motherboard and use a custom address decoder PROM to make it appear in the upper memory area. As with the 386-based...

10 KB (1,414 words) - 23:54, 5 May 2025

Instruction cycle (redirect from Fetch-decode-execute cycle)

The instruction cycle (also known as the fetch–decode–execute cycle, or simply the fetch–execute cycle) is the cycle that the central processing unit (CPU)...

10 KB (1,255 words) - 07:48, 24 April 2025