Explicitly parallel instruction computing (EPIC) is a term coined in 1997 by the HP–Intel alliance to describe a computing paradigm that researchers had...

8 KB (879 words) - 17:44, 6 November 2024

related explicitly parallel instruction computing concepts, in which multiple execution units are used to execute multiple instructions in parallel. Out-of-order...

9 KB (1,026 words) - 00:26, 27 January 2025

No instruction set computing (NISC) is a computing architecture and compiler technology for designing highly efficient custom processors and hardware...

9 KB (909 words) - 00:27, 5 December 2024

8 instructions, but is clearly a CISC because it combines memory access and computation in the same instructions. Explicitly parallel instruction computing...

15 KB (1,980 words) - 13:28, 15 November 2024

parallelism (ILP). A VLIW processor allows programs to explicitly specify instructions to execute in parallel, whereas conventional central processing units (CPUs)...

24 KB (3,038 words) - 22:21, 26 January 2025

tarpit Reduced instruction set computer Complex instruction set computer Explicitly parallel instruction computing Minimal instruction set computer Very...

31 KB (3,772 words) - 06:37, 24 March 2025

Michael S.; Rau, B. Ramakrishna (February 2000). "EPIC: Explicitly Parallel Instruction Computing". Computer. 33 (2): 37–45. doi:10.1109/2.820037. Shaout...

35 KB (4,309 words) - 09:15, 10 April 2025

of parallel computing: bit-level, instruction-level, data, and task parallelism. Parallelism has long been employed in high-performance computing, but...

74 KB (8,381 words) - 00:50, 25 April 2025

EOL—End of Line EOM—End of Message EOS—End of Support EPIC—Explicitly Parallel Instruction Computing EPROM—Erasable Programmable Read-Only Memory ERD—Entity–Relationship...

92 KB (6,587 words) - 22:31, 24 March 2025

of reduced instruction set computer (RISC) chips. Explicitly parallel instruction computing No instruction set computing One-instruction set computer...

58 KB (6,885 words) - 16:35, 25 March 2025

Superscalar processor (category Parallel computing)

very long instruction word (VLIW), explicitly parallel instruction computing (EPIC), simultaneous multithreading (SMT), and multi-core computing. With VLIW...

14 KB (1,684 words) - 11:17, 9 February 2025

Single instruction, multiple data (SIMD) is a type of parallel processing in Flynn's taxonomy. SIMD describes computers with multiple processing elements...

35 KB (4,251 words) - 08:12, 25 April 2025

Complex instruction set computer Explicitly parallel instruction computing Reduced instruction set computer Very long instruction word No instruction set...

12 KB (1,403 words) - 00:36, 13 November 2024

Concurrent computing is a form of computing in which several computations are executed concurrently—during overlapping time periods—instead of sequentially—with...

29 KB (3,004 words) - 17:17, 16 April 2025

designed Elbrus-3 computer using an architecture named Explicitly Parallel Instruction Computing (EPIC). From 1992 to 2004, Babayan held senior positions...

5 KB (450 words) - 11:23, 2 November 2024

Evolutionary Process for Integrating COTS-Based Systems Explicitly parallel instruction computing, a CPU architecture design philosophy Expansion via Prediction...

6 KB (805 words) - 07:54, 11 March 2025

RS/6000 and, more recently, have contributed to the Explicitly Parallel Instruction Computing (EPIC) computing paradigm used by Intel and HP in the Itanium processors...

21 KB (3,196 words) - 17:34, 10 April 2025

Wide-issue (category Parallel computing)

determines which instructions are ready and safe to dispatch on each clock cycle. Out-of-order execution Explicitly parallel instruction computing "Scheduling...

1 KB (130 words) - 15:59, 5 February 2021

particular tasks. Usually heterogeneity in the context of computing refers to different instruction-set architectures (ISA), where the main processor has...

15 KB (1,634 words) - 03:38, 12 November 2024

IA-64 (category Very long instruction word computing)

a variation of VLIW design concepts which Intel named explicitly parallel instruction computing (EPIC). Intel's goal was to leverage the expertise HP...

29 KB (3,189 words) - 19:59, 27 April 2025

Vector processor (category Parallel computing)

Data) and realized with VLIW (Very Long Instruction Word) and EPIC (Explicitly Parallel Instruction Computing). The Fujitsu FR-V VLIW/vector processor...

61 KB (8,675 words) - 10:31, 28 April 2025

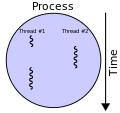

Multithreading (computer architecture) (category Parallel computing)

to further exploit instruction-level parallelism have stalled since the late 1990s. This allowed the concept of throughput computing to re-emerge from...

13 KB (1,559 words) - 20:42, 14 April 2025

Parallel Thread Execution (PTX or NVPTX) is a low-level parallel thread execution virtual machine and instruction set architecture used in Nvidia's Compute...

6 KB (572 words) - 22:58, 20 March 2025

common goal for their work. The terms "concurrent computing", "parallel computing", and "distributed computing" have much overlap, and no clear distinction...

57 KB (6,666 words) - 18:52, 16 April 2025

for each lane in parallel. The main SIMD instruction set extensions that have been introduced for x86 are: The count of 13 instructions for SSE3 includes...

131 KB (5,487 words) - 08:09, 4 May 2025

particular register as an accumulator in some instructions, but other instructions use register numbers for explicit operand specification. Any system that uses...

13 KB (1,683 words) - 22:14, 5 February 2024

introduced the DirectCompute GPU computing API, released with the DirectX 11 API. Alea GPU, created by QuantAlea, introduces native GPU computing capabilities...

71 KB (7,033 words) - 19:15, 29 April 2025

Computer cluster (redirect from Cluster computing)

and scheduled by software. The newest manifestation of cluster computing is cloud computing. The components of a cluster are usually connected to each other...

34 KB (3,744 words) - 00:28, 3 May 2025

explicitly "shared" between threads. In Tcl each thread has one or more interpreters. In programming models such as CUDA designed for data parallel computation...

33 KB (4,052 words) - 08:04, 25 February 2025

Itanium (category Very long instruction word computing)

architecture, later named Explicitly Parallel Instruction Computing (EPIC), which differs by: having template bits which show which instructions are independent...

148 KB (13,266 words) - 14:20, 30 March 2025