A logical clock is a mechanism for capturing chronological and causal relationships in a distributed system. Often, distributed systems may have no physically...

3 KB (301 words) - 14:14, 15 February 2022

the sending process's logical clock. A vector clock of a system of N processes is an array/vector of N logical clocks, one clock per process; a local "largest...

14 KB (1,862 words) - 15:08, 1 June 2025

Lamport timestamp (redirect from Lamport logical clock)

The Lamport timestamp algorithm is a simple logical clock algorithm used to determine the order of events in a distributed computer system. As different...

12 KB (1,869 words) - 14:41, 27 December 2024

Happened-before (category Logical clock algorithms)

the happened-before relation unless they use a logical clock, like a Lamport clock or a vector clock. This allows one to design algorithms for mutual...

5 KB (744 words) - 19:34, 2 June 2025

Protocol (UDP) message passing. Lamport timestamps and vector clocks are concepts of the logical clock in distributed computing. In a wireless network, the problem...

13 KB (1,539 words) - 14:49, 6 April 2025

provides a concrete syntax to handle logical clocks. The term logical clock refers to Leslie Lamport's logical clocks and its usage in CCSL is directly inspired...

1 KB (115 words) - 19:49, 31 August 2022

A matrix clock is a mechanism for capturing chronological and causal relationships in a distributed system. Matrix clocks are a generalization of the notion...

1 KB (139 words) - 21:15, 27 March 2023

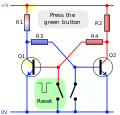

Flip-flop (electronics) (redirect from Clocked D-latch)

the master latch and clock signal. For a positive-edge triggered master–slave D flip-flop, when the clock signal is low (logical 0) the "enable" seen...

57 KB (7,211 words) - 23:43, 5 June 2025

Version vector (category Logical clock algorithms)

With Dotted Version Vectors. ACM PODC, pp. 335-336, 2012. Why Logical Clocks are Easy (Compares Causal Histories, Vector Clocks and Version Vectors)...

5 KB (716 words) - 22:21, 9 May 2023

Why Logical Clocks Are Easy. Comm. ACM 59(4), pp. 43–47, April 2016. Charron-Bost, Bernadette (July 1991), "Concerning the size of logical clocks in distributed...

13 KB (1,695 words) - 19:45, 10 June 2025

site's name, and the current timestamp of the system according to its logical clock (which is assumed to be synchronized with the other sites) Receiving...

3 KB (427 words) - 19:26, 15 November 2024

timestamps (node bootstrap time) Version numbers (logical clock values) The system uses vector clocks to track information currency and ignore outdated...

24 KB (1,961 words) - 16:50, 29 May 2025

The engine also exploits a Hybrid Logical Clock that combines coarsely-synchronized physical clocks with Lamport clocks to track causal relationships. The...

20 KB (1,406 words) - 12:45, 9 May 2025

Synchronous circuit (category Clock signal)

the next clock occurs, so the behaviour of the whole circuit can be predicted exactly. Practically, some delay is required for each logical operation...

3 KB (352 words) - 16:11, 20 December 2024

"The Part-Time Parliament". These papers relate to such concepts as logical clocks (and the happened-before relationship) and Byzantine failures. They...

18 KB (1,616 words) - 18:41, 27 April 2025

distributed systems (e.g. the bakery algorithm). Developed the concept of a logical clock, enabling synchronization between distributed entities based on the...

68 KB (1,578 words) - 15:10, 19 June 2025

Bitwise operation (redirect from Bitwise logical operation)

bitwise NOT, or bitwise complement, is a unary operation that performs logical negation on each bit, forming the ones' complement of the given binary...

31 KB (3,832 words) - 16:45, 16 June 2025

synchronous algorithms in asynchronous systems. Logical clocks provide a causal happened-before ordering of events. Clock synchronization algorithms provide globally...

57 KB (6,666 words) - 18:52, 16 April 2025

January 16, 2016. Retrieved March 18, 2014. Lamport, L. (1978). "Time, clocks, and the ordering of events in a distributed system" (PDF). Communications...

80 KB (3,581 words) - 00:11, 20 June 2025

for bit synchronization when a separate clock signal is not available. Since NRZ is not inherently a self-clocking signal, some additional synchronization...

13 KB (1,567 words) - 09:42, 29 March 2025

site. ts refers to the local time stamp of the system according to its logical clock Requesting site: A requesting site P i {\displaystyle P_{i}} sends a...

5 KB (798 words) - 04:11, 18 May 2025

reliable operations a computer can execute in a single second: logical error rates, clock speed, and number of reliable qubits. The quantities included...

4 KB (362 words) - 20:57, 8 May 2025

exclusion algorithm and its related version, this algorithm does not use logical clocks. This method requires only O(log(number of processes in the network))...

886 bytes (94 words) - 12:36, 30 June 2023

These have the property that either Data or Strobe changes its logical value in one clock cycle, but never both. More precisely data is transmitted as-is...

2 KB (233 words) - 12:16, 28 January 2024

Mengenlehreuhr (redirect from Berlin Clock)

The Mengenlehreuhr (German for "Set Theory Clock") or Berlin-Uhr ("Berlin Clock") is the first public clock in the world that tells the time by means of...

5 KB (624 words) - 02:40, 6 February 2025

Arithmetic logic unit (redirect from Arithmetical and logical unit)

next clock, are allowed to propagate through the ALU and to the destination register while the CPU waits for the next clock. When the next clock arrives...

27 KB (3,326 words) - 20:14, 20 June 2025

Instructions per cycle (redirect from Instructions Per Clock)

called instructions per clock, is one aspect of a processor's performance: the average number of instructions executed for each clock cycle. It is the multiplicative...

5 KB (596 words) - 03:55, 6 February 2025

Logic gate (redirect from Logical gate)

A logic gate is a device that performs a Boolean function, a logical operation performed on one or more binary inputs that produces a single binary output...

42 KB (3,649 words) - 19:28, 10 June 2025

Central processing unit (redirect from Logical processor)

of these early synchronous CPUs ran at low clock rates compared to modern microelectronic designs. Clock signal frequencies ranging from 100 kHz to 4 MHz...

101 KB (11,429 words) - 06:34, 17 June 2025

of the CS Request messages sent to all nodes Not based on Lamport’s logical clock The algorithm uses sequence numbers instead Used to keep track of outdated...

5 KB (767 words) - 17:23, 10 May 2025