A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from...

100 KB (13,792 words) - 09:19, 6 August 2025

Central processing unit (redirect from Cpu)

components. Modern CPUs devote a lot of semiconductor area to caches and instruction-level parallelism to increase performance and to CPU modes to support...

101 KB (11,440 words) - 12:10, 10 August 2025

When the cache client (a CPU, web browser, operating system) needs to access data presumed to exist in the backing store, it first checks the cache. If an...

30 KB (4,140 words) - 14:32, 9 August 2025

address-translation cache. It is a part of the chip's memory-management unit (MMU). A TLB may reside between the CPU and the CPU cache, between CPU cache and the...

25 KB (3,338 words) - 15:22, 30 June 2025

requested data is cached in high-speed access memory stores, allowing swifter access by central processing unit (CPU) cores. Cache hierarchy is a form...

24 KB (3,176 words) - 14:43, 24 June 2025

science, cache coloring (also known as page coloring) is the process of attempting to allocate free pages that are contiguous from the CPU cache's point...

4 KB (404 words) - 20:50, 28 July 2023

Epyc (section CPU generations)

support for larger amounts of RAM, support for ECC memory, and larger CPU cache. They also support multi-chip and dual-socket system configurations by...

39 KB (4,263 words) - 05:34, 6 August 2025

In computing, cache replacement policies (also known as cache replacement algorithms or cache algorithms) are optimizing instructions or algorithms which...

38 KB (4,885 words) - 03:55, 10 August 2025

with newer computers cache is built into either the CPU or the motherboard. COASt modules decoupled the motherboard from its cache, allowing varying configurations...

4 KB (577 words) - 23:21, 19 July 2025

List of AMD Ryzen processors (redirect from List of AMD Ryzen CPUs)

the CPUs support DDR4-2933 in dual-channel mode. L1 cache: 96 KB (32 KB data + 64 KB instruction) per core. L2 cache: 512 KB per core. All the CPUs support...

15 KB (7,387 words) - 16:21, 27 July 2025

and hardware complexity Within the L1 cache of the NetBurst CPUs, Intel incorporated its execution trace cache. It stores decoded micro-operations, so...

10 KB (1,250 words) - 07:01, 21 July 2025

Hash table (section Caching and locality of reference)

entail CPU cache inefficiencies. In cache-conscious variants of collision resolution through separate chaining, a dynamic array found to be more cache-friendly...

55 KB (6,166 words) - 20:31, 9 August 2025

List of Intel processors (redirect from Intel CPUs)

16 KB L1 cache 256 KB integrated L2 cache 60 MHz system bus clock rate Variants 150 MHz 0.35 μm process technology, (two die, a 0.35 μm CPU with 0.6 μm...

205 KB (13,785 words) - 05:44, 6 August 2025

List of Intel Core processors (redirect from Core 2 cpus)

L1 cache: 64 KB (32 KB data + 32 KB instructions) per core. L2 cache: 256 KB per core. In addition to the Smart Cache (L3 cache), Haswell-H CPUs also...

497 KB (14,119 words) - 05:44, 6 August 2025

Glossary of computer hardware terms (redirect from Cache way)

component compromises the way another component works. cache A small and fast buffer memory between the CPU and the main memory. Reduces access time for frequently...

39 KB (4,596 words) - 21:01, 1 February 2025

very fast memory known as a CPU cache which holds recently accessed data. As long as the data that the CPU needs is in the cache, the performance is much...

14 KB (1,850 words) - 04:51, 18 July 2025

primary storage and static random-access memory (SRAM) used mainly for CPU cache. Most semiconductor memory is organized into memory cells each storing...

29 KB (3,273 words) - 09:28, 5 July 2025

Cache placement policies are policies that determine where a particular memory block can be placed when it goes into a CPU cache. A block of memory cannot...

16 KB (2,179 words) - 22:24, 8 December 2024

Meltdown (security vulnerability) (redirect from Rogue data cache load)

on Security and Privacy warned against a covert timing channel in the CPU cache and translation lookaside buffer (TLB). This analysis was performed under...

87 KB (8,241 words) - 05:47, 6 August 2025

is a program optimization approach motivated by efficient usage of the CPU cache, often used in video game development. The approach is to focus on the...

5 KB (581 words) - 12:57, 10 January 2025

CPUID (redirect from CPU flag (x86))

49h indicates a level-3 cache on GenuineIntel Family 0Fh Model 6 (Pentium 4 based Xeon) CPUs, and a level-2 cache on other CPUs. Intel's CPUID documentation...

238 KB (13,505 words) - 17:54, 9 August 2025

Direct memory access (section Cache coherency)

problems. Imagine a CPU equipped with a cache and an external memory that can be accessed directly by devices using DMA. When the CPU accesses location...

28 KB (3,924 words) - 17:05, 11 July 2025

In CPU design, the use of a sum-addressed decoder (SAD) or sum-addressed memory (SAM) decoder is a method of reducing the latency of the CPU cache access...

13 KB (2,076 words) - 21:31, 12 April 2023

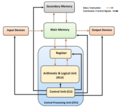

Computer architecture (redirect from CPU architecture)

particular processor will implement the ISA. The size of a computer's CPU cache for instance, is an issue that generally has nothing to do with the ISA...

27 KB (3,259 words) - 02:35, 27 July 2025

clock speed compared to flagship Intel CPU lines, such as the Pentium or Core brands. They often have less cache or intentionally disabled advanced features...

57 KB (6,125 words) - 05:31, 6 August 2025

frequency as well as the potentially present CPU cache. It is not usable for performance comparisons among different CPUs. In 1993, Lars Wirzenius posted a Usenet...

10 KB (1,009 words) - 04:54, 25 November 2024

Processor design (redirect from CPU Architecture)

now dominates the project schedule of a CPU. Key CPU architectural innovations include index register, cache, virtual memory, instruction pipelining,...

21 KB (2,416 words) - 05:53, 6 August 2025

CoreWare CW33300-based core MIPS R3000A-compatible 32-bit RISC CPU MIPS R3051 with 5 KB L1 cache, running at 33.8688 MHz. The microprocessor was manufactured...

13 KB (1,174 words) - 15:04, 9 February 2025

Overhead (computing) (section CPU caches)

function calls. In a CPU cache, the "cache size" (or capacity) refers to how much data a cache stores. For instance, a "4 KB cache" is a cache that holds 4 KB...

7 KB (831 words) - 15:50, 30 December 2024