The instruction cycle (also known as the fetch–decode–execute cycle, or simply the fetch–execute cycle) is the cycle that the central processing unit (CPU)...

10 KB (1,255 words) - 07:48, 24 April 2025

instructions per cycle (IPC), commonly called instructions per clock, is one aspect of a processor's performance: the average number of instructions executed...

5 KB (596 words) - 03:55, 6 February 2025

In computer architecture, cycles per instruction (aka clock cycles per instruction, clocks per instruction, or CPI) is one aspect of a processor's performance:...

6 KB (914 words) - 16:41, 2 October 2024

one stage for each step of the von Neumann cycle: Fetch the instruction, fetch the operands, do the instruction, write the results. A pipelined computer...

21 KB (2,571 words) - 01:33, 10 July 2024

elements involved in executing the instruction. In the instruction cycle, the instruction is loaded into the instruction register after the processor fetches...

2 KB (239 words) - 08:51, 12 February 2024

Execution (computing) (section Instruction cycle)

"fetch–decode–execute" cycle for each instruction done by the control unit. As the executing machine follows the instructions, specific effects are produced...

15 KB (1,625 words) - 19:48, 16 April 2025

instruction cycle is very rigid, and runs exactly as specified by the programmer. In the instruction fetch part of the cycle, the value of the instruction pointer...

3 KB (324 words) - 22:38, 5 April 2024

Program counter (redirect from Instruction pointer)

sections. Branch prediction Instruction cache Instruction cycle Instruction unit Instruction pipeline Instruction register Instruction scheduling Program status...

12 KB (1,382 words) - 01:18, 14 April 2025

system which provided instruction stepping Instrumentation (computer programming) Instruction set simulator Program status word Instruction cycle v t e...

3 KB (343 words) - 05:14, 30 June 2019

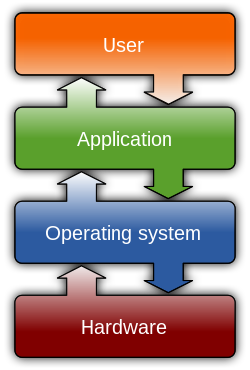

Central processing unit (redirect from Instruction decoder)

collectively known as the instruction cycle. After the execution of an instruction, the entire process repeats, with the next instruction cycle normally fetching...

101 KB (11,424 words) - 13:27, 20 May 2025

flower parts may be arranged Menstrual cycle Cycles, a render engine for the software Blender Instruction cycle, the time period during which a computer...

5 KB (580 words) - 07:37, 25 April 2025

In computer science, an instruction set architecture (ISA) is an abstract model that generally defines how software controls the CPU in a computer or...

35 KB (4,313 words) - 17:23, 20 May 2025

{\text{clock}}\times {\frac {\text{Is}}{\text{cycle}}}} However, the instructions/cycle measurement depends on the instruction sequence, the data and external factors...

64 KB (3,327 words) - 16:35, 20 May 2025

COP8 (section Instruction set)

byte, and most 1-byte instructions operate in one instruction cycle. Some, particularly branch instructions, take one or two cycles more. Some models include...

25 KB (1,324 words) - 04:14, 7 January 2025

Microarchitecture (category Instruction processing)

the control logic, the combination of cycle counter, cycle state (high or low) and the bits of the instruction decode register determine exactly what...

27 KB (3,576 words) - 18:07, 24 April 2025

Signetics 8X300 (section Instruction set)

execute an instruction in only 250 ns. Data could be input from one device, modified, and output to another device during one instruction cycle. In 1982...

14 KB (1,804 words) - 12:22, 1 December 2024

ARM architecture family (redirect from Arm instruction set)

register-register move) instructions, so that, for example, the statement in C language: a += (j << 2); could be rendered as a one-word, one-cycle instruction: ADD Ra...

142 KB (13,704 words) - 17:41, 14 May 2025

one branch. Each of them can issue one instruction per basic instruction cycle, but can have several instructions in process. These are what correspond...

2 KB (268 words) - 01:34, 16 April 2025

instruction per clock cycle, a superscalar processor can execute or start executing more than one instruction during a clock cycle by simultaneously dispatching...

14 KB (1,684 words) - 11:17, 9 February 2025

some high-performance CISC "supercomputers" in order to reduce the instruction cycle time (despite the complications of implementing within the limited...

15 KB (1,980 words) - 13:28, 15 November 2024

topic of: Multi Cycle Processors A multi-cycle processor is a processor that carries out one instruction over multiple clock cycles, often without starting...

2 KB (165 words) - 15:17, 10 October 2020

Out-of-order execution (redirect from Instruction dispatch)

execution) is an instruction scheduling paradigm used in high-performance central processing units to make use of instruction cycles that would otherwise...

36 KB (4,220 words) - 15:27, 28 April 2025

Very long instruction word (VLIW) refers to instruction set architectures that are designed to exploit instruction-level parallelism (ILP). A VLIW processor...

24 KB (3,038 words) - 22:21, 26 January 2025

computer's instruction stream", thus seeking to deliver an average throughput approaching one instruction per cycle for any single instruction stream. Other...

59 KB (6,970 words) - 03:21, 16 May 2025

fetch and decode instructions, as well as load data operands from memory (as part of the instruction cycle), to execute the instructions constituting the...

20 KB (1,788 words) - 22:05, 11 May 2025

PIC microcontrollers (section Instruction set)

instruction cycles. External interrupts have to be synchronized with the four-clock instruction cycle, otherwise there can be a one instruction cycle...

68 KB (8,354 words) - 11:38, 24 January 2025

Delay slot (category Instruction processing)

intermediate states of the instruction as it flows through the units. While this does not improve the cycle timing of any single instruction, the idea is to allow...

18 KB (2,471 words) - 13:21, 15 April 2025

serviced. The processor samples the interrupt input signal during each instruction cycle. The processor will recognize the interrupt request if the signal...

43 KB (5,520 words) - 15:52, 4 March 2025

COP400 (section Instruction set)

technology. It was typically packaged in 24- or 28-pin DIP packages. Instruction cycle time of the faster family members is 4 microseconds. The COP400 family...

35 KB (2,841 words) - 16:45, 22 April 2025

Wider instruction fetch, up to 6 instructions/cycle (From 4 instructions/cycle) Execution engine Wider instruction fetch, Up to 6 instructions/cycle (From...

13 KB (991 words) - 13:01, 8 January 2025