The interrupt priority level (IPL) is a part of the current system interrupt state, which indicates the interrupt requests that will currently be accepted...

5 KB (696 words) - 19:24, 24 August 2024

Spl (Unix) (category Interrupts)

change the interrupt priority level. This was historically needed to synchronize critical sections of kernel code that should not be interrupted. Newer Unix...

3 KB (318 words) - 18:14, 5 October 2023

IRQL (Windows) (redirect from Interrupt request level)

are sent to an interrupt controller. The interrupt controller sends an interrupt request (or IRQ) to the CPU with a certain priority level, and the CPU...

3 KB (320 words) - 19:28, 11 February 2024

(privilege level) for the duration of the interrupt handler's execution. In general, hardware interrupts and their handlers are used to handle high-priority conditions...

13 KB (1,799 words) - 05:59, 15 April 2025

Laboratory TX-2 system (1957) was the first to provide multiple levels of priority interrupts. Interrupt signals may be issued in response to hardware or software...

46 KB (5,737 words) - 02:50, 20 June 2025

Processing Language, a programming language Interrupt priority level, a part of the current system interrupt state Instituto Politécnico de Leiria, a technical...

2 KB (303 words) - 22:09, 1 May 2025

appropriate interrupt handler (ISR) after the PIC assesses the IRQs' relative priorities. Common modes of interrupt priority include hard priorities, rotating...

4 KB (424 words) - 17:15, 6 April 2025

Bellmac 32 (section Interrupt handling)

selection of a suitable interrupt handler involves a table of PCB pointers in a fixed virtual memory location. Four privilege levels are supported by the...

20 KB (1,770 words) - 13:36, 12 June 2025

priority. By properly choosing the highest priority of any interrupt that ever entered the critical section, the priority inversion problem could be solved without...

9 KB (1,155 words) - 17:46, 22 March 2025

instruction set was important. In time, as more programs were written in high-level programming languages, the instruction set became less visible, and the...

32 KB (3,030 words) - 02:49, 26 February 2025

non-maskable interrupt (NMI), despite having the highest priority among interrupts, can be prevented from occurring through the use of an interrupt mask. An...

8 KB (995 words) - 08:46, 14 June 2025

Applications of priority encoders include their use in interrupt controllers (to allow some interrupt requests to have higher priority than others), decimal...

9 KB (945 words) - 16:42, 19 May 2025

higher priority needs servicing; called preemptive priority, or priority scheduling. Time-sharing – switches tasks on a regular clocked interrupt, and on...

16 KB (2,275 words) - 03:27, 20 June 2025

well, such as more specialized flags, interrupt enable bits, and similar types of information. During an interrupt, the status of the thread currently executing...

9 KB (804 words) - 01:24, 30 May 2025

Deferred Procedure Call (category Interrupts)

system mechanism which allows high-priority tasks (e.g. an interrupt handler) to defer required but lower-priority tasks for later execution. This permits...

3 KB (423 words) - 00:22, 3 April 2024

Scheduling (computing) (redirect from Scheduling priority)

priority. The recalculation of the running thread's priority value at each clock interrupt means that a thread may lose control because its priority value...

43 KB (5,397 words) - 12:47, 27 April 2025

two interrupt link registers (ILINK) and one branch link register (BLINK). The two interrupt link registers were ILINK1 (for level 1 (low priority) maskable...

6 KB (655 words) - 03:19, 19 January 2025

Retrieved 2019-07-25. s = splnet(); "splx(9) — modify system interrupt priority level". NetBSD, OpenBSD. Retrieved 2019-07-25. Matthew Dillon (2019-07-22)...

7 KB (738 words) - 00:23, 12 October 2024

an inter-processor interrupt (IPI), also known as a shoulder tap, is a special type of interrupt by which one processor may interrupt another processor...

4 KB (378 words) - 20:54, 8 September 2024

granted priority over further cards. Interrupts can be delivered to the Interrupt Fielding Processor at any of four interrupt priority levels. Within...

11 KB (1,262 words) - 17:04, 24 May 2025

Intel 8259 (category Interrupts)

combines multiple interrupt input sources into a single interrupt output to the host microprocessor, extending the interrupt levels available in a system...

11 KB (1,618 words) - 14:58, 21 April 2025

Message precedence (redirect from Flash priority)

of the letter "O" comes from the original name for this level, "operational immediate". PRIORITY (P) is reserved for all traffic requiring expeditious action...

8 KB (822 words) - 22:28, 18 November 2024

and system space sections which are common to all processes. 32 interrupt priority levels which are used for synchronization. Hardware support for delivering...

104 KB (9,197 words) - 01:39, 11 June 2025

guest interrupt control and then started a real-time scheduler. Tasks were assigned static priorities and scheduling was originally purely priority driven...

14 KB (1,735 words) - 20:49, 12 July 2024

first-person roguelike action dungeon crawler video game developed by Priority Interrupt. It was released for Microsoft Windows, macOS, and Linux on February...

10 KB (781 words) - 01:18, 21 June 2025

IRQL may refer to: Interrupt request level, the priority of an interrupt request IRQL (Windows), a concept in the Windows NT kernel This disambiguation...

196 bytes (53 words) - 20:44, 28 December 2019

external interrupts and is referred to as the task-priority register (TPR). The AMD64 architecture allows software to define up to 15 external interrupt-priority...

38 KB (1,706 words) - 18:26, 9 January 2025

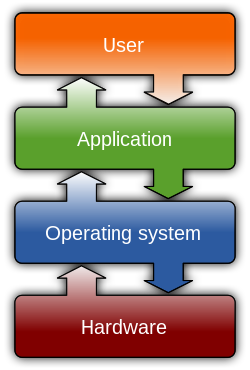

Operating system (section Software interrupt)

movement generates an interrupt called Interrupt-driven I/O. An interrupt-driven I/O occurs when a process causes an interrupt for every character or...

70 KB (8,176 words) - 14:39, 31 May 2025

Microcontroller (section Interrupt latency)

the ARMv6 architecture. Interrupt nesting. Some microcontrollers allow higher priority interrupts to interrupt lower priority ones. This allows software...

44 KB (5,266 words) - 12:50, 16 June 2025

Nord-10 (section Interrupt system)

acting on each page and one on the mode of instructions. The interrupt system had 16 program levels in hardware, each with its own set of general-purpose registers...

10 KB (1,358 words) - 22:15, 10 May 2025