Quad Data Rate (QDR) SRAM is a type of static RAM computer memory that can transfer up to four words of data in each clock cycle. Like Double Data-Rate...

3 KB (510 words) - 08:07, 28 January 2023

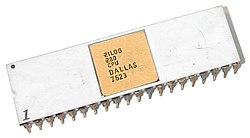

Static random-access memory (redirect from SRAM latency)

double data rate I/O. Quad Data Rate SRAM – synchronous, separate read and write ports, quadruple data rate I/O. Single-stack SRAM 2.5D SRAM – as of...

27 KB (3,295 words) - 02:57, 12 July 2025

construction does. 1T-SRAM has speed comparable to 6T-SRAM (at multi-megabit densities). It is significantly faster speed than eDRAM, and the "quad-density" variant...

7 KB (840 words) - 16:27, 29 January 2025

Serial Peripheral Interface (redirect from Quad SPI)

has same abbreviation as Quad SPI described in § Quad SPI) is a type of SPI controller that uses a data queue to transfer data across an SPI bus. It has...

51 KB (5,946 words) - 14:45, 4 August 2025

AVR microcontrollers (section Internal data memory)

external data space has been enhanced to support both SRAM and SDRAM. As well, the data addressing modes have been expanded to allow up to 16 MB of data memory...

63 KB (7,497 words) - 11:31, 25 July 2025

link used in high-performance computing Quad Data Rate SRAM, a type of computer memory that transfers data using QDR Quadrennial Defense Review, a former...

966 bytes (185 words) - 04:00, 27 August 2024

D-cache), 512 KB flash, 16 KB ITCM SRAM + 64 KB DTCM SRAM + 192 KB SRAM + 4 KB battery-back‡ SRAM, 0.5 KB OTP, quad-SPI memory interface. NUCLEO-F746ZG...

117 KB (8,524 words) - 17:23, 4 August 2025

32 KB ISP flash memory with read-while-write capabilities, 1 KB EEPROM, 2 KB SRAM, 23 general-purpose I/O lines, 32 general-purpose working registers, 3 flexible...

8 KB (548 words) - 01:53, 22 July 2025

1975 Cray-1, and was the world's fastest computer from 1983 to 1985 with a quad-processor system performance of 800 MFLOPS. The principal designer was Steve...

10 KB (1,158 words) - 15:31, 29 December 2024

Xeon (redirect from Quad-Core Xeon)

custom 512 kB SRAMs developed by Intel. The number of SRAMs depended on the amount of cache. A 512 kB configuration required one SRAM, a 1 MB configuration:...

117 KB (7,857 words) - 06:04, 6 August 2025

associative cache separated into 2×64 KB for data and instructions (a concept from Harvard architecture). SRAM cache designs at the time were incapable of...

50 KB (5,066 words) - 05:29, 6 August 2025

PA-8000 (section Data cache)

Systems Enhanced SRAM (ESRAM) chips, which despite its name, is an implementation of 1T-SRAM – dynamic random access memory (DRAM) with a SRAM-like interface...

22 KB (3,114 words) - 07:16, 4 August 2025

as on-chip SRAM, to manage data and minimize power consumption. Additionally, some SSDs use an SLC buffer mechanism to temporarily store data in single-level...

128 KB (11,183 words) - 05:58, 6 August 2025

technology first emerged in the mid-2000s. In 2004, IBM demonstrated a 0.143 μm2 SRAM cell with a poly gate pitch of 135 nm, produced using electron-beam lithography...

12 KB (1,221 words) - 05:24, 6 August 2025

many transistors per cell as a standard SRAM so it allows for a larger cache while using the same area as SRAM. The technical specification further specifies:...

20 KB (1,800 words) - 05:52, 6 August 2025

Central processing unit (section Clock rate)

Data Center Definitions. SearchDataCenter.com. Archived from the original on 5 August 2010. Retrieved 8 August 2016. Mlblevins (8 April 2010). "Quad Core...

101 KB (11,434 words) - 05:49, 18 July 2025

data becomes unreadable. These formats include built-in error correction mechanisms, which function by adding redundant data. However, once the rate of...

68 KB (6,996 words) - 04:55, 26 June 2025

Rockchip products. RK3399 was the flagship SoC of Rockchip, Dual A72 and Quad A53 and Mali-T860MP4 GPU, providing high computing and multi-media performance...

62 KB (4,459 words) - 18:10, 5 July 2025

QA—Quality assurance QC—Quality control QC—Quick Charge QDR—Quad Data Rate QEMU—Quick Emulator QFP—Quad Flat Package QoS—Quality of Service QOTD—Quote of the...

118 KB (8,346 words) - 17:20, 5 August 2025

3-layer metal 108-pin ceramic quad flat package (QFP) 1.5 million transistors, 8KB L1 instruction cache, 8KB L1 data cache, compatible with IDT 79R3081E...

17 KB (1,158 words) - 02:19, 6 June 2025

DDR5-5200 in quad-channel mode while Threadripper PRO CPUs support DDR5-5200 in octa-channel mode with ECC support. L1 cache: 64 KB (32 KB data + 32 KB instruction)...

33 KB (4,442 words) - 06:04, 6 August 2025

100 Gbit/s RoCE interfaces for networking 4x HBM2E, 1.2 TB/s bandwidth 3D-SRAM stacked below AI SoC die 1228 mm2 Total die size (456 mm2 Virtuvian AI SoC...

79 KB (4,964 words) - 05:38, 6 August 2025

interconnect. The two levels of polysilicon enabled IDT to use a four-transistor SRAM cell, resulting in a transistor count of 3.6 million and a die that measured...

12 KB (1,816 words) - 03:46, 23 July 2025

but more expensive static RAM (SRAM) and the slower but cheaper dynamic RAM (DRAM). When an SoC has a cache hierarchy, SRAM will usually be used to implement...

43 KB (4,744 words) - 21:56, 28 July 2025

static random-access memory (SRAM), as well as two major NVM types: flash memory and read-only memory (ROM). Typical CMOS SRAM consists of six transistors...

238 KB (10,581 words) - 06:00, 6 August 2025

unless SRAM, more expensive and less dense (but faster), was used. Non-multiplexed buses (the 8080 had state signals multiplexed onto the data bus). A...

118 KB (12,641 words) - 17:10, 15 June 2025

25 MHz i486 part. An 8 KB on-chip (level 1) SRAM cache stores the most recently used instructions and data (16 KB and/or write-back on some later models)...

47 KB (4,390 words) - 22:19, 14 July 2025

supported FPM and EDO DRAM, SRAM, flash, and ROM. The PCMCIA controller supports two slots. The memory address and data bus is shared with the PCMCIA...

20 KB (2,622 words) - 22:38, 26 June 2025

shaders : Texture mapping units : Render output units 2 The effective data transfer rate of GDDR5 is quadruple its nominal clock, instead of double as it is...

195 KB (16,850 words) - 05:26, 6 August 2025

Serial Peripheral Interface ports, two megabytes of flash memory, 256KB of SRAM, and three 32-bit timers. It operates at 100 MHz. It is advised for usage...

154 KB (15,934 words) - 05:55, 6 August 2025