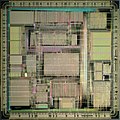

SPARC (Scalable Processor ARChitecture) is a reduced instruction set computer (RISC) instruction set architecture originally developed by Sun Microsystems...

77 KB (6,335 words) - 19:43, 28 June 2025

The ANSI-SPARC Architecture (American National Standards Institute, Standards Planning And Requirements Committee), is an abstract design standard for...

4 KB (559 words) - 18:37, 8 April 2024

The SPARC Enterprise series is a range of UNIX server computers based on the SPARC V9 architecture. It was co-developed by Sun Microsystems and Fujitsu...

11 KB (988 words) - 08:51, 27 May 2025

dedicated cryptographic unit per core. The cores use the 64-bit SPARC Version 9 architecture running at frequencies between 2.85 GHz and 3.0 GHz, and are...

11 KB (1,013 words) - 22:10, 16 April 2025

x86 architecture as well as several 8-bit architectures are little-endian. Most RISC architectures (SPARC, Power, PowerPC, MIPS) were originally big-endian...

34 KB (1,849 words) - 19:41, 3 July 2025

SPARC T5 is the fifth generation multicore microprocessor of Oracle's SPARC T series family. It was first presented at Hot Chips 24 in August 2012, and...

9 KB (666 words) - 22:10, 16 April 2025

ISBN 978-0-12-374493-7. Patterson, David; Hennessy, John (2011). Computer Architecture: A Quantitative Approach (5th ed.). Morgan Kaufmann. ISBN 978-0-12-383872-8...

10 KB (1,237 words) - 18:00, 7 July 2025

SPARC (Scalable Processor Architecture) is a computer instruction set architecture. SPARC may also refer to: Scholarly Publishing and Academic Resources...

2 KB (229 words) - 05:50, 9 October 2024

The SPARC T-series family of RISC processors and server computers, based on the SPARC V9 architecture, was originally developed by Sun Microsystems, and...

11 KB (759 words) - 22:14, 16 April 2025

Sun to implement the 64-bit SPARC V9 instruction set architecture (ISA). Marc Tremblay was a co-microarchitect. The UltraSPARC is a four-issue superscalar...

4 KB (492 words) - 22:09, 16 April 2025

NX bit (category X86 architecture)

Architectural Manual, Version 8". SPARC International. p. 244. The SPARC Architecture Manual, Version 9 (PDF). SPARC International. 1994. F.3.2 Attributes...

10 KB (1,167 words) - 12:37, 3 May 2025

new-from-the-ground-up SPARC microprocessor implementation that conforms to the UltraSPARC Architecture 2005 specification and executes the full SPARC V9 instruction...

20 KB (2,691 words) - 22:09, 16 April 2025

between registers).: 9–12 Some RISC architectures such as PowerPC, SPARC, RISC-V, ARM, and MIPS are load–store architectures.: 9–12 For instance, in a load–store...

2 KB (194 words) - 10:35, 3 November 2024

The microSPARC (code-named Tsunami) is a discontinued microprocessor implementing the SPARC V8 instruction set architecture (ISA), developed by Sun Microsystems...

3 KB (159 words) - 22:08, 16 April 2025

Reduced instruction set computer (redirect from RISC architecture)

as the MIPS and SPARC systems. IBM eventually produced RISC designs based on further work on the 801 concept, the IBM POWER architecture, PowerPC, and Power...

62 KB (7,270 words) - 23:22, 6 July 2025

VAX-11/784 superminicomputer. The only systems that beat it were the Sun SPARC and MIPS R2000 RISC-based workstations. Further, as the CPU was designed...

142 KB (13,724 words) - 19:52, 15 June 2025

exception occurs SPARC International, Inc. The SPARC Architecture Manual, Version 9. PTR Prentice Hall. Sun Microsystems. UltraSPARC Architecture 2005. Draft...

25 KB (3,338 words) - 15:22, 30 June 2025

Sun Microsystems (section SPARC-based systems)

computer servers and workstations built on its own RISC-based SPARC processor architecture, as well as on x86-based AMD Opteron and Intel Xeon processors...

88 KB (8,631 words) - 05:13, 29 June 2025

The UltraSPARC III, code-named "Cheetah", is a microprocessor that implements the SPARC V9 instruction set architecture (ISA) developed by Sun Microsystems...

9 KB (1,258 words) - 22:11, 19 February 2025

fourth generation of UltraSPARC microprocessors, and implement the 64-bit SPARC V9 instruction set architecture (ISA). The UltraSPARC IV was originally to...

6 KB (554 words) - 22:09, 16 April 2025

OpenSPARC is an open-source hardware project, started in December 2005, for CPUs implementing the SPARC instruction architecture. The initial contribution...

3 KB (263 words) - 11:15, 16 June 2025

reconfigured as needed. SPARC hypervisors run in hyperprivileged execution mode, which was introduced in the sun4v architecture. The sun4v processors released...

15 KB (1,865 words) - 23:27, 28 January 2023

The SPARC T3 microprocessor (previously known as UltraSPARC T3, codenamed Rainbow Falls and also referred to as UltraSPARC KT or Niagara-3 during development)...

15 KB (1,159 words) - 16:23, 7 July 2025

and SPARC uses "output register 7" or o7. In some others, such as PA-RISC, RISC-V, and the IBM System/360 and its successors, including z/Architecture, the...

6 KB (655 words) - 03:19, 19 January 2025

enforcing page coloring, which is described below. Some early RISC processors (SPARC, RS/6000) took this approach. It has not been used recently, as the hardware...

99 KB (13,735 words) - 12:24, 8 July 2025

The SuperSPARC is a microprocessor that implements the SPARC V8 instruction set architecture (ISA) developed by Sun Microsystems. 33 and 40 MHz versions...

4 KB (227 words) - 22:08, 16 April 2025

is a proliferation of side-channel attacks plaguing modern computer architectures. Many of these attacks measure slight, nondeterministic variations in...

22 KB (2,135 words) - 18:53, 16 May 2025

the in and out instructions found on microprocessors based on the x86 architecture. Different forms of these two instructions can copy one, two or four...

17 KB (2,288 words) - 01:44, 18 November 2024

The UltraSPARC II, code-named "Blackbird", is a microprocessor implementation of the SPARC V9 instruction set architecture (ISA) developed by Sun Microsystems...

5 KB (577 words) - 22:09, 16 April 2025

Microsystems' UltraSPARC T2 microprocessor is a multithreading, multi-core CPU. It is a member of the SPARC family, and the successor to the UltraSPARC T1. The chip...

10 KB (1,332 words) - 13:00, 4 July 2025