HyperTransport (HT), formerly known as Lightning Data Transport, is a technology for interconnection of computer processors. It is a bidirectional serial/parallel...

21 KB (2,371 words) - 17:47, 2 November 2024

The HyperTransport Consortium is an industry consortium responsible for specifying and promoting the computer bus technology called HyperTransport. The...

2 KB (157 words) - 05:40, 6 November 2024

dual-channel architecture, doubling peak memory bandwidth, and the HyperTransport bus was increased in speed from 800 MHz to 1000 MHz. Socket 939 also...

52 KB (5,383 words) - 16:17, 3 April 2025

CPUs communicate using the Direct Connect Architecture over high-speed HyperTransport links. Each CPU can access the main memory of another processor, transparent...

43 KB (4,918 words) - 19:27, 19 September 2024

Motherboards: One HyperTransport 3.x link between CPU with 2.2 GHz, two HT 2.x links with 1 GHz for I/O operations Socket Fr6 Three Hypertransport 3.x links with...

3 KB (362 words) - 13:02, 23 March 2024

64-bit single channel on-die DDR-400 memory controller, and an 800 MHz HyperTransport bus. Battery saving features, like PowerNow!, are central to the marketing...

21 KB (2,288 words) - 00:58, 15 April 2025

PowerNow! Technology (Cool’n’Quiet Technology) HyperTransport Technology (not the same as Intel Hyper-Threading Technology) Processors with an "e" following...

8 KB (663 words) - 21:45, 19 January 2025

allowing for modification of the CPU speed without changing the FSB or HyperTransport. On a non-black edition CPU, the multiplier is allowed to only be lowered...

23 KB (2,508 words) - 02:40, 25 February 2024

Refresh CPUs: K8 core, HyperTransport 1.0, DDR2 memory Socket S1g2 Platforms: Puma and Yukon CPUs: K8 Revision G core, HyperTransport 3.0, DDR2 memory Added:...

3 KB (261 words) - 02:25, 28 August 2023

Athlon 64, including an integrated (on-die) memory controller, the HyperTransport link, and AMD's "NX bit" feature. In the second half of 2005, AMD added...

17 KB (1,354 words) - 14:22, 22 March 2025

the coauthor of the specifications for the x86-64 instruction set and HyperTransport interconnect. From 2012 to 2015 he returned to AMD to work on the AMD...

16 KB (1,196 words) - 01:10, 16 April 2025

differences between Socket AM2 and AM2+ socket processors are as follows: HyperTransport 3.0 operating at up to 2.6 GHz Split power planes: one for the CPU cores...

6 KB (632 words) - 21:20, 19 May 2025

package, supporting both unbuffered or buffered DDR3 (with Socket G3MX), HyperTransport 3.0 and IOMMU, all of them forming the codenamed "Piranha" server platform...

14 KB (1,084 words) - 23:34, 25 April 2024

SSE2, SSE3, SSE4a, AMD64, Cool'n'Quiet, NX bit, AMD-V Socket AM2+, HyperTransport with 1600 to 2000 MHz Power consumption (TDP): 65, 95, 125 and 140 Watt...

12 KB (884 words) - 06:34, 14 December 2024

Improvements in system interconnect: HyperTransport retry support Support for HyperTransport 3.0, with HyperTransport Link unganging which creates 8 point-to-point...

78 KB (5,521 words) - 02:03, 29 March 2025

SSE3 (revision E or later) instruction sets. It features one 16 bit HyperTransport link running up to 1000 MT/s. In regards to video expansion slots, Socket...

4 KB (426 words) - 21:14, 19 May 2025

designed around a 64-bit ISA, added an integrated memory controller, HyperTransport communication fabric, L2 cache sizes up to 1 MB (1128 KB total cache)...

11 KB (1,142 words) - 01:48, 18 November 2024

support of AM3+ CPUs, AMD has validated the 9-Series chipset for use with HyperTransport 3.1 (up to 6.4 GT/s). They also worked with NVIDIA to bring SLI support...

6 KB (668 words) - 06:04, 26 January 2025

intermediate successor to socket AM2, which features split power planes, and HyperTransport 3.0. Socket AM2+ chips can plug into a socket AM2 motherboard (although...

5 KB (541 words) - 21:13, 19 May 2025

include: HyperTransport – a high-bandwidth, low-latency system bus used in AMD's CPU and APU products Infinity Fabric – a derivative of HyperTransport used...

156 KB (15,974 words) - 22:43, 5 May 2025

2009. Allan McNaughton (September 29, 2003). "AMD HyperTransport Bus: Transport Your Application to Hyper Performance". AMD. Archived from the original on...

20 KB (1,820 words) - 10:57, 2 October 2024

dual-core PowerPC G5 configurations, which can communicate through its HyperTransport at half its internal clock speed. Each processor in the Power Mac G5...

30 KB (2,582 words) - 10:46, 15 May 2025

have been an inspiration for other more recent technologies, such as HyperTransport. QuickRing started as an offshoot of the fabled Futurebus project, which...

6 KB (925 words) - 01:36, 19 May 2024

HyperTransport is used, running at 800 MHz for Semprons. The multipliers here apply to the 200 MHz system clock frequency, not the HyperTransport speed...

28 KB (861 words) - 14:45, 18 January 2025

Extended 3DNow!, SSE, SSE2, SSE3, AMD64, Cool'n'Quiet, NX Bit Socket 939, HyperTransport (1000 MHz, HT1000) VCore: 1.35–1.4 V Power use (TDP): 89 Watt First...

16 KB (1,536 words) - 09:39, 17 May 2025

with dynamic routing capabilities. It was designed to compete with HyperTransport that had been used by Advanced Micro Devices (AMD) since around 2003...

18 KB (2,096 words) - 23:02, 10 February 2025

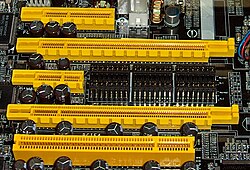

extinct language of Anatolia ZIC3, a protein HyperTransport Expansion connector, part of the HyperTransport specification This disambiguation page lists...

664 bytes (98 words) - 20:25, 16 December 2023

processor's interrupt register in memory space.[citation needed] The HyperTransport protocol also supports MSI. While more complex to implement in a device...

13 KB (1,535 words) - 16:49, 7 May 2024

buses have been emerging into the market since about 2001, including HyperTransport and InfiniBand. They also tend to be very flexible in terms of their...

31 KB (3,928 words) - 14:02, 5 May 2025

CPU) 940 (Bulldozer Based CPU) FSB protocol HyperTransport 3.1 FSB frequency 200 MHz System clock HyperTransport up to 3.2 GHz Processors Phenom II Athlon...

6 KB (548 words) - 21:08, 19 May 2025