In computing, an opcode (abbreviated from operation code) is an enumerated value that specifies the operation to be performed. Opcodes are employed in...

17 KB (1,169 words) - 22:24, 15 July 2025

Machine code (redirect from Opcode-level programming)

machine code opcodes and operands are replaced with mnemonics and labels. For example, the x86 architecture has available the 0x90 opcode; it is represented...

38 KB (3,880 words) - 10:47, 24 July 2025

An opcode table (also called an opcode matrix) is a visual representation of all opcodes in an instruction set. It is arranged such that each axis of...

9 KB (213 words) - 22:08, 27 February 2025

computing, an opcode prefix is an numeric value that alters the function of a following opcode. On some instruction set architectures multiple opcode prefixes...

6 KB (780 words) - 18:23, 27 July 2025

X86 instruction listings (redirect from ARPL (opcode))

PREFETCHW, opcode 0F 0D /0 as well as opcodes 0F 0D /2../7 are all documented to be performing prefetch. On Intel processors with PREFETCHW, these opcodes are...

265 KB (15,000 words) - 22:03, 26 July 2025

Opcode Systems, Inc. was founded in 1985 by Dave Oppenheim and based in and around Palo Alto, California, USA. Opcode produced MIDI sequencing software...

10 KB (936 words) - 01:49, 29 June 2024

Assembly language (redirect from Opcode mnemonics)

uses a mnemonic to represent, e.g., each low-level machine instruction or opcode, each directive, typically also each architectural register, flag, etc....

89 KB (9,904 words) - 01:25, 4 August 2025

The Intel BCD opcodes are a set of six x86 instructions that operate with binary-coded decimal numbers. The radix used for the representation of numbers...

10 KB (1,363 words) - 23:07, 6 March 2025

SIGTRAP. The opcode for INT3 is 0xCC, as opposed to the opcode for INT immediate8, which is 0xCD immediate8. Since the dedicated 0xCC opcode has some desired...

4 KB (478 words) - 16:42, 24 July 2025

Fetching the instruction opcodes from program memory well in advance is known as prefetching and it is served by using a prefetch input queue (PIQ). The...

12 KB (1,695 words) - 22:00, 30 July 2023

An illegal opcode, also called an unimplemented operation, unintended opcode or undocumented instruction, is an instruction to a CPU that is not mentioned...

10 KB (922 words) - 05:00, 28 May 2025

Metasploit (redirect from Opcode Database)

against a remote target machine. Other important sub-projects include the Opcode Database, shellcode archive and related research. The Metasploit Project...

17 KB (1,623 words) - 19:04, 20 July 2025

instructions. On the processing architecture, a given instruction may specify: opcode (the instruction to be performed) e.g. add, copy, test any explicit operands:...

35 KB (4,329 words) - 19:12, 27 June 2025

CHIP-8 (section Opcode table)

the semantics of a few of the opcodes, and SCHIP continued to use those new semantics in addition to changing other opcodes. Many online resources about...

22 KB (1,886 words) - 16:12, 5 June 2025

initial opcode byte, followed by up to 2 bytes of operands. 1⁄4 of the opcode bytes, x0–x3, are used for irregular opcodes. 3⁄4 of the opcode bytes, x4–xF...

58 KB (6,421 words) - 14:05, 2 August 2025

design flaw was discovered by programmers. Due to incomplete opcode decoding, two illegal opcodes, 0x9D and 0xDD, will cause the program counter on the processor...

26 KB (2,677 words) - 13:11, 25 May 2025

Arithmetic logic unit (section Opcode)

called operands, and a code indicating the operation to be performed (opcode); the ALU's output is the result of the performed operation. In many designs...

27 KB (3,326 words) - 20:14, 20 June 2025

code or opcode for short). The command to add two numbers together would have one opcode; the command to multiply them would have a different opcode, and...

140 KB (14,116 words) - 06:41, 28 July 2025

Instruction cycle (redirect from Opcode fetch)

operations based on specific opcodes in the instruction. For example, in RISC-V architecture, funct3 and funct7 opcodes exist to distinguish whether an...

10 KB (1,248 words) - 15:20, 16 July 2025

Open Music System (OMS) was a virtual studio management application by Opcode for the Classic Mac OS. Similar to FreeMIDI by Mark of the Unicorn and Audio...

896 bytes (82 words) - 03:30, 24 January 2024

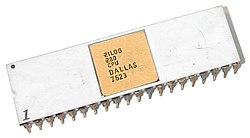

registers. The binary opcodes (machine language) were identical, but preceded by a new opcode prefix. Zilog published the opcodes and related mnemonics...

118 KB (12,641 words) - 17:10, 15 June 2025

(immediate), and J (jump). Every instruction starts with a 6-bit opcode. In addition to the opcode, R-type instructions specify three registers, a shift amount...

70 KB (8,083 words) - 19:26, 27 July 2025

assigned by the program that generates any kind of query. QR - Query/Response. OPCODE - A 4-bit field that specifies the kind of query in this message. This value...

4 KB (406 words) - 07:07, 22 February 2024

effects; for example, on the Motorola 68000 series of processors, the NOP opcode causes a synchronization of the pipeline. Listed below are the NOP instruction...

39 KB (2,420 words) - 15:36, 22 July 2025

the same on all Art-Net packets, while the green portion is variable. The opcode (given in little endian) tells the recipient this is a packet containing...

7 KB (591 words) - 08:38, 3 August 2025

to: STOS BASIC, a programming language for the Atari ST computer stos, an opcode mnemonic in X86 assembly language Secure Trusted Operating System Consortium...

420 bytes (90 words) - 10:21, 18 October 2017

with one or more operands to translate into one or more bytes known as an opcode. RISC-V processors feature a set of registers that serve as storage for...

4 KB (306 words) - 20:40, 13 March 2025

TEST (x86 instruction) (section TEST opcode variations)

flags are set to 0, while AF flag is undefined. There are 9 different opcodes for the TEST instruction depending on the type and size of the operands...

2 KB (276 words) - 09:15, 3 May 2025

X86 assembly language (section Mnemonics and opcodes)

human-readable compared to raw machine code. Each machine code instruction is an opcode which, in assembly is replaced with a mnemonic. Each mnemonic corresponds...

57 KB (6,649 words) - 02:57, 2 August 2025