Pipelining is an important technique used in several applications such as digital signal processing (DSP) systems, microprocessors, etc. It originates...

6 KB (1,036 words) - 01:00, 17 April 2024

Pipelining may refer to: Pipeline (computing), aka a data pipeline, a set of data processing elements connected in series Protocol pipelining, a technique...

759 bytes (126 words) - 13:25, 10 November 2023

transformation technique using in DSP architecture implementation for minimizing the number of functional blocks in synthesizing DSP architecture. Folding was...

8 KB (1,343 words) - 17:42, 23 May 2021

parallel processing and pipelining techniques, it is better to choose parallel processing techniques with the following reasons Pipelining usually causes I/O...

6 KB (1,058 words) - 21:44, 1 February 2024

technique of duplicating the functional blocks to increase the throughput of the DSP program in such a way that preserves its functional behavior at its outputs...

8 KB (1,304 words) - 11:37, 19 November 2022

predictable. Graphics pipeline, the method of rasterization-based rendering as supported by graphics hardware Pipelining (DSP implementation), a transformation...

4 KB (543 words) - 00:50, 13 July 2025

engineering, instruction pipelining is a technique for implementing instruction-level parallelism within a single processor. Pipelining attempts to keep every...

21 KB (2,571 words) - 19:47, 13 July 2025

Digital signal processor (redirect from DSP Chip)

(DSP) is a specialized microprocessor chip, with its architecture optimized for the operational needs of digital signal processing.: 104–107 DSPs are...

26 KB (2,924 words) - 08:07, 4 March 2025

Delay slot (section Pipelining)

instruction located immediately after a branch instruction on a RISC or DSP architecture; this instruction will execute even if the preceding branch...

18 KB (2,471 words) - 13:21, 15 April 2025

Very long instruction word (section Implementations)

steps so the instructions can be executed partly at the same time (termed pipelining), dispatching individual instructions to be executed independently, in...

24 KB (3,038 words) - 22:21, 26 January 2025

video. The DSP module comprises a set of instructions and state in the integer pipeline and requires minimal additional logic to implement in MIPS processor...

70 KB (8,083 words) - 08:05, 18 July 2025

suitable for integration with other SIP cores (e.g. GPU, display controller, DSP, image processor, etc.) into one die constituting a system on a chip (SoC)...

5 KB (381 words) - 12:48, 17 May 2025

TMS320 (redirect from TI TMS320C54x DSP)

processors (DSPs) from Texas Instruments. It was introduced on April 8, 1983, through the TMS32010 processor, which was then the fastest DSP on the market...

20 KB (2,240 words) - 11:24, 18 July 2025

link register). Fixed instruction width of 32 bits to ease decoding and pipelining, at the cost of decreased code density. Later, the Thumb instruction set...

142 KB (13,724 words) - 19:52, 15 June 2025

with deeply out of order, speculative issue 3-way superscalar execution pipeline DSP and NEON SIMD extensions are mandatory per core VFPv4 Floating Point...

6 KB (477 words) - 16:58, 18 February 2024

Microarchitecture (section Instruction pipelining)

modern Intel and AMD processors, are implemented with both microcode and pipelines. Improvements in pipelining and caching are the two major microarchitectural...

27 KB (3,576 words) - 23:42, 21 June 2025

(DSPs) have used multi-core architectures for much longer than high-end general-purpose processors. A typical example of a DSP-specific implementation...

52 KB (5,788 words) - 06:30, 10 June 2025

OpenRISC 1200 (section CPU/DSP)

modified by any individual. The official implementation is maintained by developers at OpenCores.org. The implementation specifies a power management unit,...

6 KB (655 words) - 01:15, 4 February 2025

Processor design (section Implementation logic)

lessen the implementation burden by acquiring some of these items by purchasing them as intellectual property. Control logic implementation techniques...

21 KB (2,408 words) - 22:01, 25 April 2025

Saturation arithmetic (section Implementations)

result can be a catastrophic loss in signal-to-noise ratio in a DSP system. Signals in DSP designs are therefore usually either scaled appropriately to avoid...

8 KB (1,081 words) - 08:19, 14 June 2025

90% greater performance. Pipelined processor with deeply out-of-order, speculative issue 3-way superscalar execution pipeline DSP and NEON SIMD extensions...

5 KB (436 words) - 16:31, 23 August 2024

added a DSP extension, then called SH-3-DSP. With extended data paths for efficient DSP processing, special accumulators and a dedicated MAC-type DSP engine...

23 KB (2,794 words) - 14:50, 10 June 2025

Messerschmitt, D.G. (July 1989). "Pipeline Interleaving and Parallelism in Recursive Digital Filters, Part I: Pipelining using Scattered Look-Ahead and Decomposition"...

25 KB (2,458 words) - 15:53, 5 June 2025

high clock rates were achieved through the method of deep pipelining (called super-pipelining then). The improved R4400 followed in 1993. It had larger...

29 KB (3,615 words) - 03:46, 19 July 2025

Parallel multidimensional digital signal processing (section Parallel implementations of multidimensional discrete fourier transforms)

Parallel multidimensional digital signal processing (mD-DSP) is defined as the application of parallel programming and multiprocessing to digital signal...

23 KB (3,692 words) - 20:09, 27 June 2025

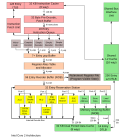

System on a chip (section Pipelining)

scheduling algorithms. Hardware and software tasks are often pipelined in processor design. Pipelining is an important principle for speedup in computer architecture...

43 KB (4,745 words) - 17:50, 2 July 2025

integer divide, and saturation arithmetic instructions. The Cortex-M4 adds DSP instructions and an optional single-precision floating-point unit (VFPv4-SP)...

82 KB (5,908 words) - 14:52, 8 July 2025

characteristics of that implementation, providing binary compatibility between implementations. This enables multiple implementations of an ISA that differ...

35 KB (4,329 words) - 19:12, 27 June 2025

CPU cache (section Implementation)

the MIPS R6000 uses this cache type as the sole known implementation. The R6000 is implemented in emitter-coupled logic, which is an extremely fast technology...

99 KB (13,735 words) - 12:24, 8 July 2025

suitable for integration with other SIP cores (e.g. GPU, display controller, DSP, image processor, etc.) into one die constituting a system on a chip (SoC)...

4 KB (296 words) - 07:35, 7 May 2024