The interrupt descriptor table (IDT) is a data structure used by the x86 architecture to implement an interrupt vector table. The IDT is used by the processor...

8 KB (1,201 words) - 01:51, 20 May 2025

affected by an interrupt, it looks up the interrupt handler in the interrupt vector table, and transfers control to it. Interrupt descriptor table (x86 Architecture...

5 KB (492 words) - 01:28, 4 November 2024

compatibility problems of BIOS and protected mode. DOS interrupt call Interrupt descriptor table Ralf Brown's Interrupt List Not all computers with BIOS are IBM PC...

29 KB (3,319 words) - 17:50, 25 July 2024

accessing descriptor tables such as the Global Descriptor Table (GDT), the Interrupt descriptor table (IDT) and the Local Descriptor Table (LDT). Segment...

12 KB (1,285 words) - 22:37, 11 July 2025

The Global Descriptor Table (GDT) is a core part of Intel's x86 architecture that helps manage how memory is accessed and protected. Introduced with the...

6 KB (738 words) - 08:13, 19 May 2025

the table of interrupt descriptors, which normally resides on a single memory page, is instead split over two pages such that the descriptors for the...

12 KB (1,583 words) - 03:50, 19 June 2025

Task state segment (redirect from Interrupt Stack Table)

the Interrupt Stack Table (IST), which also resides in the TSS and contains logical (segment+offset) stack pointers. If an interrupt descriptor table specifies...

10 KB (1,543 words) - 08:58, 23 June 2025

Context switch (section Interrupt handling)

JMP instruction targeted at a TSS descriptor in the global descriptor table. It can occur implicitly when an interrupt or exception is triggered if there...

15 KB (1,963 words) - 07:06, 23 February 2025

transducer, a sensor and transmitter for a surface acoustic wave Interrupt descriptor table, a memory structure of x86 microprocessors Insulation-displacement...

1 KB (192 words) - 20:26, 16 February 2023

Win16 applications can do TSR-like tricks such as patching the interrupt descriptor table (IDT) because Windows allowed it. Windows Me does not allow a...

13 KB (1,802 words) - 03:34, 7 July 2025

device driver which writes over the interrupt descriptor table (IDT). If the IDT is corrupted, when the next interrupt happens, the processor will be unable...

5 KB (549 words) - 17:08, 11 July 2025

processor state that are normally outside of the IA-32 API scope, like descriptor cache registers. The LOADALL for 286 processors is encoded 0Fh 05h, while...

23 KB (1,731 words) - 09:24, 27 May 2025

descriptors used by the LGDT, LIDT, SGDT and SIDT instructions consist of a 2-part data structure. The first part is a 16-bit value, specifying table...

265 KB (15,000 words) - 22:03, 26 July 2025

code written in C for 16-bit real-mode x86 devices may write the interrupt descriptor table (IDT) at physical address 0 of the machine by dereferencing a...

17 KB (2,095 words) - 02:51, 20 July 2025

ISO 9660 (section Volume descriptor set)

The rest begins with a volume descriptor set (a header block which describes the subsequent layout) and then the path tables, directories and files on the...

49 KB (5,843 words) - 14:50, 24 July 2025

include: Modifying system service descriptor tables Modifying the interrupt descriptor table Modifying the global descriptor table Using kernel stacks not allocated...

24 KB (2,113 words) - 02:32, 21 December 2024

into a descriptor table that is stored in memory. There are two such tables, the Global Descriptor Table (GDT) and the Local Descriptor Table (LDT), each...

105 KB (10,906 words) - 21:35, 26 July 2025

2006.156. S2CID 99779. "The Descriptor" (PDF). Bitsavers. "Unisys Descriptor". Unisys. "Pbits". Unisys. "Pbit interrupt". Unisys. Daniel H. H. Ingalls...

49 KB (7,099 words) - 18:50, 8 May 2025

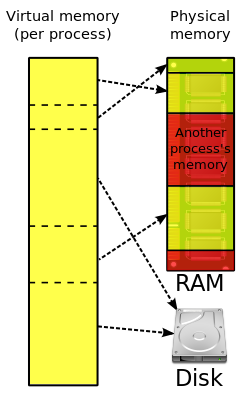

Virtual memory (section Page tables)

the same real address. This mode is used for interrupt mechanisms, for the paging supervisor and page tables in older systems, and for application programs...

43 KB (5,351 words) - 14:51, 13 July 2025

reads the 64-bit segment descriptor structure from either the Global Descriptor Table when TI=0 or the Local Descriptor Table when TI=1. It then performs...

23 KB (3,302 words) - 13:26, 24 June 2025

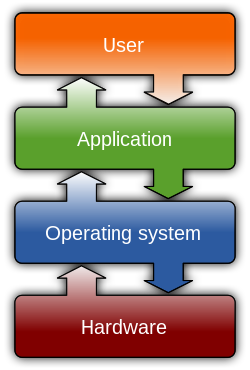

Operating system (section Software interrupt)

given a security descriptor. Later releases have added even more security features. Comparison of operating systems DBOS Interruptible operating system...

70 KB (8,177 words) - 07:24, 23 July 2025

limitations which may be revealed when ChatGPT responds to prompts including descriptors of people. In one instance, ChatGPT generated a rap in which women and...

171 KB (15,047 words) - 02:22, 3 August 2025

create a pointer (copy descriptor) from a base (MOM) descriptor NXLN Index and load name (resulting in an indexed descriptor) NXLV Index and load value...

29 KB (4,040 words) - 08:21, 8 May 2023

program, the T field of an Operand Call or Descriptor Call syllable is relative to the Program Reference Table (PRT). For subroutines, the type of addressing...

89 KB (10,512 words) - 10:40, 26 July 2025

makes this memory available through the Global Descriptor Table (GDT) and one or more Local Descriptor Tables (LDTs). The memory is "protected" in the sense...

9 KB (1,148 words) - 16:26, 10 July 2025

X86 virtualization (redirect from Advanced Virtual Interrupt Controller)

get the descriptors back from the processor. Shadow descriptor tables must therefore be used to track changes made to the descriptor tables by the guest...

41 KB (3,747 words) - 04:38, 30 July 2025

Native API calls are handled by the kernel via the System Service Descriptor Table (SSDT). The Native API comprises many functions. They include C runtime...

6 KB (679 words) - 04:13, 2 July 2025

Protected mode may only be entered after the system software sets up one descriptor table and enables the Protection Enable (PE) bit in the control register...

48 KB (4,357 words) - 21:14, 21 July 2025

below 16 MB). The value of the CS register at reset is F000h with the descriptor base set to FF0000h and the value of the IP register at reset is FFF0h...

9 KB (1,028 words) - 19:02, 4 September 2024

special selector value to reference a descriptor accessed via the Global Descriptor Table or the Local Descriptor Table, which contains the information needed...

5 KB (765 words) - 22:36, 6 February 2023