Clock rate or clock speed in computing typically refers to the frequency at which the clock generator of a processor can generate pulses used to synchronize...

13 KB (1,611 words) - 00:46, 29 March 2025

DDR SDRAM (redirect from Double-data-rate synchronous dynamic random access memory)

rate" refers to the fact that a DDR SDRAM with a certain clock frequency achieves nearly twice the bandwidth of a SDR SDRAM running at the same clock...

26 KB (2,512 words) - 13:13, 1 June 2025

using the clock signal for synchronization may become active at either the rising edge, falling edge, or, in the case of double data rate, both in the...

18 KB (2,248 words) - 20:57, 12 April 2025

Quad data rate (QDR, or quad pumping) is a communication signaling technique wherein data are transmitted at four points in the clock cycle: on the rising...

4 KB (510 words) - 17:16, 8 June 2024

Die size: 111 mm2 (Conroe) Steppings: ? These models feature an unlocked clock multiplier All models support: MMX, SSE, SSE2, SSE3, SSSE3, Enhanced Intel...

497 KB (14,118 words) - 16:45, 30 May 2025

accurately, real clocks will differ after some amount of time due to clock drift, caused by clocks counting time at slightly different rates. There are several...

13 KB (1,539 words) - 14:49, 6 April 2025

system bus clock rate Variants 150 MHz (60 MHz bus clock rate, 256 KB 0.6 μm cache) introduced November 1, 1995 166 MHz (66 MHz bus clock rate, 512 KB 0...

199 KB (13,736 words) - 22:13, 25 May 2025

The molecular clock is a figurative term for a technique that uses the mutation rate of biomolecules to deduce the time in prehistory when two or more...

32 KB (3,696 words) - 18:30, 24 May 2025

(400–1066 MT/s using a 200–533 MHz I/O clock) and four times the rate of DDR (200–400 MT/s using a 100–200 MHz I/O clock). High-performance graphics was an...

32 KB (3,310 words) - 12:18, 30 May 2025

The summary for this series is: Core: ARM Cortex-M0 core at a maximum clock rate of 48 MHz. Cortex-M0 options include the SysTick Timer. Memory: Static...

111 KB (7,833 words) - 03:21, 12 April 2025

Central processing unit (section Clock rate)

of these early synchronous CPUs ran at low clock rates compared to modern microelectronic designs. Clock signal frequencies ranging from 100 kHz to 4 MHz...

101 KB (11,424 words) - 02:20, 1 June 2025

clock cycle. Since the DDR2 internal clock runs at half the DDR external clock rate, DDR2 memory operating at the same external data bus clock rate as...

18 KB (1,876 words) - 02:31, 17 April 2025

and Pentium-branded ones support only SSE4.1/4.2. 350 MHz base graphics clock rate No L4 cache (eDRAM) A release date of January 3, 2017 Features common...

55 KB (2,526 words) - 08:16, 28 May 2025

Socket AM4 TDP: 35 W First release: September 6, 2018 CPU clock rate: 3.2 to 3.5 GHz GPU clock rate: 1000 to 1100 MHz Mendocino (6 nm) (see the list article...

49 KB (4,986 words) - 09:03, 28 May 2025

efficiency. DDR4 speeds are advertised as double the base clock rate due to its Double Data Rate (DDR) nature, with common speeds including DDR4-2400 and...

49 KB (4,577 words) - 06:47, 5 March 2025

Clock drift refers to several related phenomena where a clock does not run at exactly the same rate as a reference clock. That is, after some time the...

8 KB (1,073 words) - 02:12, 9 February 2025

There has been a clock speed regression for Lion Cove P-cores in Arrow Lake-S desktop processors. The Core Ultra 9 285K has a peak clock speed of 5.7 GHz...

47 KB (3,244 words) - 16:20, 25 May 2025

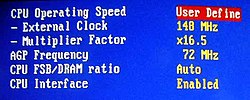

Overclocking (redirect from Clock lock)

In computing, overclocking is the practice of increasing the clock rate of a computer to exceed that certified by the manufacturer. Commonly, operating...

48 KB (5,969 words) - 19:27, 22 March 2025

clock rate while remaining under the card's predetermined power budget. Multiple boost clocks are available, but this table lists the highest clock supported...

481 KB (13,342 words) - 00:13, 3 June 2025

Single-precision performance is calculated from the base (or boost) core clock speed based on a FMA operation. Manufacturer suggested retail price at launch...

15 KB (7,041 words) - 19:11, 30 May 2025

cycles in Zen 2 to 46 clock cycles and halves per-core cache bandwidth, although both problems are partially mitigated by higher clock speeds. Total cache...

19 KB (3,418 words) - 15:18, 20 April 2025

alongside the Zen line of CPUs. Vega targets increased instructions per clock, higher clock speeds, and support for HBM2. AMD's Vega has new memory hierarchy...

14 KB (3,728 words) - 23:36, 13 December 2024

computing, double data rate (DDR) describes a computer bus that transfers data on both the rising and falling edges of the clock signal and hence doubles...

6 KB (634 words) - 20:17, 8 April 2025

DIN sync (section Relation to other clock systems)

DIN sync and MIDI clock outputs can act as master clock for those two formats. Though DIN sync and MIDI clock have the same clock rate, they require a conversion...

14 KB (898 words) - 08:42, 18 March 2025

only the Transmeta Crusoe. This means the controller runs at the same clock rate as the CPU, and that the electrical signals have a shorter physical distance...

52 KB (5,383 words) - 16:17, 3 April 2025

across the board (or near to it), while operating at drastically lower clock rates. Maintaining high instructions per cycle (IPC) on a deeply pipelined...

276 KB (9,895 words) - 17:34, 2 June 2025

Time dilation (redirect from Clock hypothesis)

frame moving relative to the local clock, this clock will be running (that is ticking) more slowly, since tick rate equals one over the time period between...

53 KB (6,730 words) - 14:18, 15 May 2025

Power is only guaranteed when P-Cores/E-cores do not exceed the base clock rate. Max Turbo Power: the maximum sustained (> 1 s) power dissipation of the...

58 KB (2,781 words) - 20:21, 30 May 2025

Single-precision performance is calculated from the base (or boost) core clock speed based on a FMA operation. Unified shaders : texture mapping units :...

198 KB (11,668 words) - 04:23, 19 March 2025

architecture, 300 MHz clock rate, developed by MCST Elbrus-S Elbrus-1S+ – single-core evolution of Elbrus 2000 SoC, 1000 MHz clock rate + GPU Elbrus-2S+ –...

4 KB (373 words) - 19:26, 2 April 2024