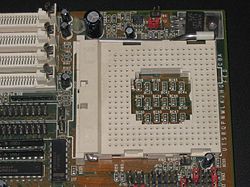

A pin grid array (PGA) is a type of integrated circuit packaging. In a PGA, the package is square or rectangular, and the pins are arranged in a regular...

10 KB (967 words) - 16:44, 20 November 2024

The land grid array (LGA) is a type of surface-mount packaging for integrated circuits (ICs) that is notable for having the pins on the socket (when a...

9 KB (1,255 words) - 16:30, 3 June 2025

BGA is descended from the pin grid array (PGA), which is a package with one face covered (or partly covered) with pins in a grid pattern which, in operation...

17 KB (2,026 words) - 09:52, 9 April 2025

List of electronic component packaging types (redirect from Pin pitch)

typically 0.5 mm Land grid array (LGA): An array of bare lands only. Similar to in appearance to QFN, but mating is by spring pins within a socket rather...

62 KB (3,442 words) - 15:44, 29 May 2025

Dual in-line package (redirect from Dual in-line pin package)

respectively) Pin grid array (PGA) packages may be considered to have evolved from the DIP. PGAs with the same 0.1 inches (2.54 mm) pin centers as most...

23 KB (3,294 words) - 23:17, 31 January 2025

Integrated circuit packaging (redirect from Area array package)

first area array package was a ceramic pin grid array package. Not long after, the plastic ball grid array (BGA), another type of area array package, became...

15 KB (1,590 words) - 06:50, 22 April 2025

last Intel desktop socket to use a pin grid array (PGA) interface. All later Intel desktop sockets use a land grid array (LGA) interface. Socket 478 was...

4 KB (355 words) - 16:24, 14 March 2025

Socket A (also known as Socket 462) is a zero insertion force pin grid array (PGA) CPU socket used for AMD processors ranging from the Athlon Thunderbird...

8 KB (729 words) - 01:05, 15 June 2025

Socket rPGA 947 has one extra pin hole, other than that it is identical to socket G3. It is the last pin grid array socket for Intel's mobile processors...

3 KB (205 words) - 00:51, 15 June 2025

chips with many pins, zero insertion force (ZIF) sockets are preferred. Common sockets include pin grid array (PGA) or land grid array (LGA). These designs...

33 KB (733 words) - 03:27, 17 June 2025

169-pin pin grid array (PGA) socket and the first with an official designation. Socket 1 was intended as a 486 upgrade socket, and added one extra pin to...

2 KB (162 words) - 03:30, 18 June 2025

ICL Integrated circuit packages: Ball grid array pin grid array land grid array Processor array Programmable Array Logic (PAL), a systematic way to implement...

4 KB (504 words) - 22:59, 23 July 2024

Pentium OverDrive processors. Socket 2 was a 238-pin zero insertion force (ZIF) 19×19 pin grid array (PGA) socket suitable for the 5-volt, 25 to 66 MHz...

1 KB (86 words) - 23:03, 24 April 2025

gate arrays to drive and receive the system bus. A custom 419-pin pin grid array (PGA) package was developed to house all bus interface gate arrays. .....

28 KB (3,561 words) - 18:02, 25 November 2024

rearranged the pin layout. Socket 3 is compatible with 168-pin socket CPUs. Socket 3 was a 237-pin zero insertion force (ZIF) 19×19 pin grid array (PGA) socket...

2 KB (138 words) - 14:51, 18 August 2024

wiring. It is packaged in a 36 mm by 36 mm ceramic pin grid array module which had 201 signal pins. It required a 3.6 volt power supply and consumed 4...

4 KB (655 words) - 23:51, 19 February 2023

L2 cache (integrated) 242-pin Slot-1 SECC2 (Single Edge Contact cartridge 2) processor package, 370-pin FC-PGA (flip-chip pin grid array) package System Bus...

199 KB (13,736 words) - 22:13, 25 May 2025

1994. Consisting of 320 pins, this was the first socket to use a staggered pin grid array, or SPGA, which allowed the chip's pins to be spaced closer together...

3 KB (232 words) - 04:25, 7 April 2024

Ridge (derived from Excavator) powered Athlon X4 and some A-Series, a pin grid array (PGA) socket that they promised to support until 2020. At CES 2022,...

10 KB (1,183 words) - 09:02, 7 April 2025

QM77 chipset. Pins arranged in a 35 × 36 grid array (it is incompatible with G1 socket due to different placing of one pin) 18 × 15 size grid removed from...

6 KB (363 words) - 07:05, 12 September 2024

in a 179-pin ceramic pin grid array (CPGA). The R4000SC and R4000MC are packaged in a 447-pin ceramic staggered pin grid array (SPGA). The pin out of the...

13 KB (1,806 words) - 15:26, 31 May 2024

memory controller The pin configuration of the AM2+ socket (940 pins) is mechanically different from the AM3 socket (941 pins) The 4 holes for fastening...

6 KB (632 words) - 21:20, 19 May 2025

(ball grid array) format. It replaces Socket 615 (μPGA1), which was used in Pentium II and early Celeron mobile processors. This socket is a 495 pin CPU...

1 KB (104 words) - 12:32, 29 May 2024

479 has 479 pin holes. Pentium M processors in PGA package have 479 pins that plug into this zero insertion force socket. Only 478 pins are electrically...

7 KB (765 words) - 11:12, 3 February 2025

P6100, P6200, P6300 Intel Celeron P4500, P4600 Pins arranged in a 36 × 35 grid array 18 × 15 size grid removed from the center Utilization of cam actuated...

5 KB (451 words) - 23:45, 28 August 2024

on personal computers. The "370" refers to the number of pin holes in the socket for CPU pins. Socket 370 was replaced by Socket 423 in 2000. Socket 370...

5 KB (447 words) - 21:57, 24 March 2024

the 386 Translator. This was a module that could be plugged into the pin-grid array socket reserved for the 80286 microprocessor on the motherboard of IBM's...

22 KB (2,493 words) - 12:35, 29 April 2025

EIST. Socket P has 478 pins, but is not electrically pin-compatible with Socket M or Socket 478. Socket P is also known as a 478-pin Micro FCPGA or μFCPGA-478...

2 KB (177 words) - 16:15, 18 August 2024

process and alignment of parts during assembly. The later pin grid array (PGA) and ball grid array (BGA) packages, by allowing connections to be made over...

10 KB (1,190 words) - 13:50, 13 June 2025

incompatible with 939 motherboards and vice versa, and although it has 940 pins, it is incompatible with Socket 940. Socket AM2 supports DDR2 SDRAM memory...

5 KB (541 words) - 21:13, 19 May 2025