ADX (Multi-Precision Add-Carry Instruction Extensions) is Intel's arbitrary-precision arithmetic extension to the x86 instruction set architecture (ISA)...

3 KB (226 words) - 06:13, 17 January 2021

Vector Extensions (AVX, also known as Gesher New Instructions and then Sandy Bridge New Instructions) are SIMD extensions to the x86 instruction set architecture...

51 KB (4,089 words) - 23:38, 15 May 2025

AVX-512 (redirect from Advanced Vector Extensions 512)

AVX-512 are 512-bit extensions to the 256-bit Advanced Vector Extensions SIMD instructions for x86 instruction set architecture (ISA) proposed by Intel...

87 KB (4,830 words) - 07:39, 12 June 2025

to cover new instruction set extensions without the OS context-switching code needing to understand the specifics of the new extensions. This is done...

263 KB (14,911 words) - 15:01, 7 May 2025

the ISA without those extensions. Machine code using those extensions will only run on implementations that support those extensions. The binary compatibility...

35 KB (4,329 words) - 14:46, 11 June 2025

ARM architecture family (redirect from Large Physical Address Extensions)

additional instruction sets for different roles: the "Thumb" extensions add both 32- and 16-bit instructions for improved code density, while Jazelle added instructions...

142 KB (13,724 words) - 17:45, 14 June 2025

otherwise they are unmodified. Add and subtract (but not rotate) instructions that set C also set the DC (digit carry) flag, the carry from bit 3 to bit 4, which...

148 KB (4,299 words) - 11:16, 24 February 2025

exchange platform merged into Google Ad Manager Intel ADX, add-carry instruction extensions in the x86 microprocessor architecture Adrenalectomy, the surgical...

1 KB (203 words) - 20:57, 7 May 2025

RISC-V (category Instruction set architectures)

128-bit Streaming SIMD Extensions (SSE), to 256-bit Advanced Vector Extensions (AVX), and AVX-512). The result is a growing instruction set, and a need to...

153 KB (15,871 words) - 06:49, 11 June 2025

CPUID (redirect from Indirect branch control extension)

to cover new instruction set extensions without the OS context-switching code needing to understand the specifics of the new extensions. This is done...

233 KB (13,252 words) - 09:05, 10 June 2025

In computer engineering, an orthogonal instruction set is an instruction set architecture where all instruction types can use all addressing modes. It...

21 KB (3,017 words) - 05:34, 20 April 2025

3DNow! (section 3DNow! extensions)

deprecated extension to the x86 instruction set developed by Advanced Micro Devices (AMD). It adds single instruction multiple data (SIMD) instructions to the...

17 KB (1,747 words) - 00:59, 3 June 2025

CHIP-8 (section CHIP-8 extensions and variations)

not specifically use the new SCHIP extensions. Some extensions take opcodes or behavior from multiple extensions, like XO-CHIP which takes some from...

22 KB (1,886 words) - 16:12, 5 June 2025

avoided the instruction encodings used by KNC's MVEX prefix, however with the introduction of Intel APX (Advanced Performance Extensions) in 2023, some...

98 KB (4,641 words) - 00:26, 21 March 2025

polynomials would not be seen as a carry-less multiplication of numbers. CLMUL instruction set, an x86 ISA extension Finite field arithmetic Galois/Counter...

5 KB (922 words) - 19:33, 2 May 2025

X86 (redirect from Advanced Performance Extensions)

APX (Advanced Performance Extensions) are extensions to double the number of general-purpose registers from 16 to 32 and add new features to improve general-purpose...

105 KB (10,798 words) - 13:47, 11 June 2025

X86 assembly language (section Instruction types)

multiply accumulation instruction (useful for software-based alpha-blending and digital filtering). SSE (since SSE3) and 3DNow! extensions include addition...

57 KB (6,615 words) - 19:32, 6 June 2025

Intel MCS-51 (section Instruction set)

effect. Only the ADD, ADDC, and SUBB instructions set PSW flags. The INC, DEC, and logical instructions do not. The CJNE instruction modifies the C bit...

58 KB (6,418 words) - 13:11, 22 May 2025

DEC Alpha (redirect from Motion Video Instructions)

load or store instructions (later added with the Byte Word Extensions (BWX)) The Alpha does not have condition codes for integer instructions to remove a...

63 KB (6,361 words) - 18:54, 23 May 2025

Intel Software Guard Extensions (SGX) is a set of instruction codes implementing trusted execution environment that are built into some Intel central processing...

22 KB (2,135 words) - 18:53, 16 May 2025

Qualcomm Hexagon (redirect from Hexagon Vector eXtensions)

programs into streams of instructions – bit streams - that the device can understand and carry out (execute). As an instruction stream executes, the integrity...

57 KB (3,064 words) - 13:00, 29 April 2025

EVEX prefix (category X86 instructions)

(enhanced vector extension) and corresponding coding scheme is an extension to the 32-bit x86 (IA-32) and 64-bit x86-64 (AMD64) instruction set architecture...

12 KB (1,161 words) - 01:33, 1 September 2024

Vector processor (section Vector instruction example)

processors include: Intel x86's MMX, SSE and AVX instructions, AMD's 3DNow! extensions, ARM NEON, Sparc's VIS extension, PowerPC's AltiVec and MIPS' MSA. In 2000...

61 KB (8,675 words) - 10:31, 28 April 2025

TI MSP430 (section MSP430X 20-bit extension)

Indexed addressing modes add a 16-bit extension word to the instruction. If both source and destination are indexed, the source extension word comes first. x...

77 KB (7,964 words) - 18:51, 17 September 2024

SPARC (section Instruction formats)

processors with a new instruction extensions set, called HPC-ACE (High Performance Computing – Arithmetic Computational Extensions). Fujitsu's K computer...

76 KB (6,257 words) - 22:08, 16 April 2025

SSE5 (redirect from Streaming SIMD Extensions version 5)

SIMD Extensions version 5) was a SIMD instruction set extension proposed by AMD on August 30, 2007 as a supplement to the 128-bit SSE core instructions in...

6 KB (626 words) - 11:38, 7 November 2024

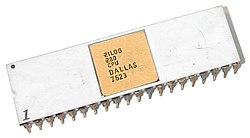

Zilog Z80 (redirect from Z80 instruction set)

instructions are available in the original Z80, though registers A and HL can be multiplied by powers of two with ADD A,A and ADD HL,HL instructions (similarly...

118 KB (12,632 words) - 15:40, 8 June 2025

PDP-11 architecture (category Instruction set architectures)

DIV, and ASHC instructions. Other 32-bit data are supported as extensions to the basic architecture: floating point in the FPU Instruction Set or long data...

52 KB (4,456 words) - 20:07, 2 April 2025

VAX (section Instruction set)

VAX (an acronym for virtual address extension) is a series of computers featuring a 32-bit instruction set architecture (ISA) and virtual memory that was...

32 KB (3,030 words) - 02:49, 26 February 2025

The Multimedia Acceleration eXtensions or MAX are instruction set extensions to the Hewlett-Packard PA-RISC instruction set architecture (ISA). MAX was...

6 KB (539 words) - 23:11, 4 August 2023