allows more CPU throughput than a multicycle computer at a given clock rate, but may increase latency due to the added overhead of the pipelining process...

21 KB (2,571 words) - 11:33, 24 June 2025

Computer-related pipelines include: Instruction pipelines, such as the classic RISC pipeline, which are used in central processing units (CPUs) and other microprocessors...

15 KB (2,207 words) - 16:47, 23 February 2025

Central processing unit (redirect from Cpu)

A central processing unit (CPU), also called a central processor, main processor, or just processor, is the primary processor in a given computer. Its...

101 KB (11,442 words) - 15:47, 23 June 2025

central processing units (RISC CPUs) used a very similar architectural solution, now called a classic RISC pipeline. Those CPUs were: MIPS, SPARC, Motorola...

24 KB (3,612 words) - 15:23, 17 April 2025

Hazard (computer architecture) (redirect from Pipeline break)

the domain of central processing unit (CPU) design, hazards are problems with the instruction pipeline in CPU microarchitectures when the next instruction...

10 KB (1,237 words) - 10:14, 13 February 2025

R800 (redirect from R800 (CPU))

Corporation of Japan and built by Mitsui & Co The goal was a modern and pipelined CPU binary compatible with the Z80, and therefore with MSX software, while...

6 KB (893 words) - 19:08, 6 January 2025

A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from...

97 KB (13,327 words) - 00:25, 25 June 2025

CPU time (or process time) is the amount of time that a central processing unit (CPU) was used for processing instructions of a computer program or operating...

9 KB (1,182 words) - 16:43, 23 May 2025

within a single CPU such as an arithmetic logic unit. While a superscalar CPU is typically also pipelined, superscalar and pipelining execution are considered...

14 KB (1,678 words) - 19:56, 4 June 2025

Instructions per second (redirect from CPU speed)

execution order and the presence of branch instructions (problematic in CPU pipelines). CPU instruction rates are different from clock frequencies, usually reported...

65 KB (3,426 words) - 18:16, 20 June 2025

devices running Android 7.1 depend on screen size and density and type of CPU, ranging from 816 MB–1.8 GB for 64-bit and 512 MB–1.3 GB for 32-bit meaning...

218 KB (11,120 words) - 12:25, 16 June 2025

Microarchitecture (redirect from CPU microarchitecture)

MIPS and SPARC designs. Most modern CPUs (even embedded CPUs) are now pipelined, and microcoded CPUs with no pipelining are seen only in the most area-constrained...

27 KB (3,576 words) - 23:42, 21 June 2025

List of Intel processors (redirect from Intel CPUs)

Hyper-Threading support is only available on CPUs using the 800 MHz system bus. The processor's integer instruction pipeline has been increased from 20 stages to...

199 KB (13,736 words) - 22:13, 25 May 2025

The following is a partial list of Intel CPU microarchitectures. The list is incomplete, additional details can be found in Intel's tick–tock model,...

52 KB (2,899 words) - 00:13, 4 May 2025

because the observer program itself affects the CPU performance (modern, heavily cached and pipelined CPUs are particularly affected by this kind of observation)...

2 KB (198 words) - 00:17, 12 February 2018

process. This can be called a multiprocessed pipeline. In this way, the scheduler will naturally switch the CPU among the processes so as to minimize its...

11 KB (1,401 words) - 17:36, 10 September 2024

Instruction cycle (redirect from CPU cycle)

the fetch–execute cycle) is the cycle that the central processing unit (CPU) follows from boot-up until the computer has shut down in order to process...

10 KB (1,255 words) - 07:48, 24 April 2025

optimization in pipelined CPUs to limit performance deficits which occur due to pipeline stalls. A data hazard can lead to a pipeline stall when the current...

4 KB (229 words) - 10:04, 13 March 2022

NetBurst (redirect from Hyper Pipelined Technology)

microarchitecture in the x86 family of central processing units (CPUs) made by Intel. The first CPU to use this architecture was the Willamette-core Pentium 4...

16 KB (1,648 words) - 01:48, 3 January 2025

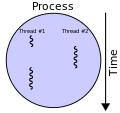

architecture, multithreading is the ability of a central processing unit (CPU) (or a single core in a multi-core processor) to provide multiple threads...

13 KB (1,559 words) - 20:42, 14 April 2025

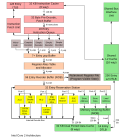

Control unit (section Pipelined control units)

control unit (CU) is a component of a computer's central processing unit (CPU) that directs the operation of the processor. A CU typically uses a binary...

30 KB (4,299 words) - 23:41, 21 June 2025

Simultaneous multithreading (redirect from Multithreaded CPU)

(SMT) is a technique for improving the overall efficiency of superscalar CPUs with hardware multithreading. SMT permits multiple independent threads of...

21 KB (2,450 words) - 00:49, 19 April 2025

a loop, and provides a default direction so that simple pipelined CPUs can fill their pipeline of instructions. Other than this, RISC-V does not require...

154 KB (15,959 words) - 08:35, 25 June 2025

may also refer to: Pipeline (computing), a chain of data-processing stages or a CPU optimization found on Instruction pipelining, a technique for implementing...

4 KB (537 words) - 02:27, 22 February 2025

Pentium (original) (redirect from 586 (CPU))

a microprocessor introduced by Intel on March 22, 1993. It is the first CPU using the Pentium brand. Considered the fifth generation in the x86 (8086)...

40 KB (3,895 words) - 17:55, 21 June 2025

to their destination. This layout reduces CPU branches, making GVE faster than VLQ on modern pipelined CPUs. PrefixVarint is a similar design but with...

16 KB (1,673 words) - 20:47, 6 November 2024

Time (Unix) (section Real time vs CPU time)

in sh, bash, tcsh or in zsh). The total CPU time is the combination of the amount of time the CPU or CPUs spent performing some action for a program...

6 KB (760 words) - 01:26, 1 November 2024

Haswell (microarchitecture) (redirect from Devil's Canyon (CPU))

shrink/tick of the Sandy Bridge microarchitecture). Intel officially announced CPUs based on this microarchitecture on June 4, 2013, at Computex Taipei 2013...

109 KB (4,974 words) - 13:06, 17 December 2024