A CPU cache is a hardware cache used by the central processing unit (CPU) of a computer to reduce the average cost (time or energy) to access data from...

96 KB (13,277 words) - 14:52, 30 April 2024

When the cache client (a CPU, web browser, operating system) needs to access data presumed to exist in the backing store, it first checks the cache. If an...

31 KB (4,302 words) - 21:19, 13 May 2024

Central processing unit (redirect from Cpu)

components. Modern CPUs devote a lot of semiconductor area to caches and instruction-level parallelism to increase performance and to CPU modes to support...

100 KB (11,315 words) - 14:15, 3 May 2024

requested data is cached in high-speed access memory stores, allowing swifter access by central processing unit (CPU) cores. Cache hierarchy is a form...

24 KB (3,167 words) - 19:30, 15 May 2024

address-translation cache. It is a part of the chip's memory-management unit (MMU). A TLB may reside between the CPU and the CPU cache, between CPU cache and the...

24 KB (3,327 words) - 05:58, 5 January 2024

Cache placement policies are policies that determine where a particular memory block can be placed when it goes into a CPU cache. A block of memory cannot...

16 KB (2,175 words) - 09:38, 2 April 2024

In computing, cache replacement policies (also known as cache replacement algorithms or cache algorithms) are optimizing instructions or algorithms which...

40 KB (5,238 words) - 04:01, 9 May 2024

very fast memory known as a CPU cache which holds recently accessed data. As long as the data that the CPU needs is in the cache, the performance is much...

14 KB (1,791 words) - 05:45, 9 May 2024

List of AMD Ryzen processors (redirect from List of AMD Ryzen CPUs)

HEDT CPUs: Socket: TR4. All the CPUs support DDR4-2933 in quad-channel mode. L1 cache: 96 KB (32 KB data + 64 KB instruction) per core. L2 cache: 512 KB...

8 KB (5,599 words) - 03:25, 11 May 2024

Meltdown (security vulnerability) (redirect from Rogue data cache load)

on Security and Privacy warned against a covert timing channel in the CPU cache and translation lookaside buffer (TLB). This analysis was performed under...

68 KB (7,221 words) - 14:30, 27 March 2024

science, cache coloring (also known as page coloring) is the process of attempting to allocate free pages that are contiguous from the CPU cache's point...

4 KB (404 words) - 20:50, 28 July 2023

Direct memory access (section Cache coherency)

problems. Imagine a CPU equipped with a cache and an external memory that can be accessed directly by devices using DMA. When the CPU accesses location...

28 KB (3,894 words) - 18:52, 15 May 2024

is a program optimization approach motivated by efficient usage of the CPU cache, often used in video game development. The approach is to focus on the...

5 KB (575 words) - 04:21, 2 May 2024

Overhead (computing) (section CPU caches)

function calls. In a CPU cache, the "cache size" (or capacity) refers to how much data a cache stores. For instance, a "4 KB cache" is a cache that holds 4 KB...

6 KB (766 words) - 21:49, 22 March 2024

Glossary of computer hardware terms (redirect from Cache way)

cache A small and fast buffer memory between CPU and Main memory. Reduces access time for frequently accessed items (instructions / operands). cache coherency...

39 KB (4,569 words) - 21:49, 25 April 2024

CoreWare CW33300-based core MIPS R3000A-compatible 32-bit RISC CPU MIPS R3051 with 5 KB L1 cache, running at 33.8688 MHz. The microprocessor was manufactured...

11 KB (1,017 words) - 15:48, 26 November 2023

Athlon's CPU cache consisted of the typical two levels. Athlon was the first x86 processor with a 128 KB split level-1 cache; a 2-way associative cache separated...

49 KB (4,910 words) - 05:46, 5 May 2024

Microprocessor (redirect from CPU chip)

it feasible to integrate memory on the same die as the processor. This CPU cache has the advantage of faster access than off-chip memory and increases...

83 KB (9,710 words) - 12:48, 17 May 2024

List of Intel processors (redirect from Intel CPUs)

16 KB L1 cache 256 KB integrated L2 cache 60 MHz system bus clock rate Variants 150 MHz 0.35 μm process technology, (two die, a 0.35 μm CPU with 0.6 μm...

178 KB (13,532 words) - 05:09, 12 May 2024

clock speed compared to flagship Intel CPU lines, such as the Pentium or Core brands. They often have less cache or intentionally disabled advanced features...

54 KB (5,855 words) - 06:56, 6 April 2024

primary storage, and static random-access memory (SRAM) used mainly for CPU cache. Most semiconductor memory is organized into memory cells each storing...

29 KB (3,270 words) - 20:53, 30 March 2024

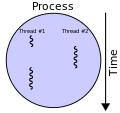

of a single or multiple cores, which include the computing units, the CPU caches, and the translation lookaside buffer (TLB). Where multiprocessing systems...

13 KB (1,562 words) - 15:53, 3 January 2024

of silicon area and cost. SRAM is typically used for the cache and internal registers of a CPU while DRAM is used for a computer's main memory. Semiconductor...

26 KB (3,155 words) - 15:25, 7 May 2024

266, 300 MHz L1 cache: 16 + 16 KB (Data + Instructions) L2 cache: 512 KB, as external chips on the CPU module clocked at half the CPU frequency. Packaging:...

23 KB (2,470 words) - 06:59, 16 May 2024

In CPU design, the use of a sum-addressed decoder (SAD) or sum-addressed memory (SAM) decoder is a method of reducing the latency of the CPU cache access...

13 KB (2,076 words) - 21:31, 12 April 2023

Non-uniform memory access (redirect from Cache coherent NUMA)

release of Skylake (2017). Nearly all CPU architectures use a small amount of very fast non-shared memory known as cache to exploit locality of reference in...

16 KB (1,617 words) - 17:27, 6 April 2024

List of Intel Core processors (redirect from Core 2 cpus)

L1 cache: 64 KB (32 KB data + 32 KB instructions) per core. L2 cache: 256 KB per core. In addition to the Smart Cache (L3 cache), Haswell-H CPUs also...

465 KB (13,365 words) - 19:54, 15 May 2024

("spindles"), since using multiple devices allows parallelism Cache space, including CPU cache and MMU cache (translation lookaside buffer) Network throughput Electrical...

4 KB (502 words) - 11:20, 4 May 2024

Sandy Bridge (redirect from Gesher (CPU architecture))

AGU per core Two load/store operations per CPU cycle for each memory channel Decoded micro-operation cache, and enlarged, optimized branch predictor Sandy...

58 KB (2,686 words) - 18:53, 12 May 2024