Explicitly parallel instruction computing (EPIC) is a term coined in 1997 by the HP–Intel alliance to describe a computing paradigm that researchers had... 7 KB (871 words) - 19:39, 23 March 2024 |

Michael S.; Rau, B. Ramakrishna (February 2000). "EPIC: Explicitly Parallel Instruction Computing". Computer. 33 (2): 37–45. doi:10.1109/2.820037. Shaout... 34 KB (4,278 words) - 05:44, 2 May 2024 |

parallelism (ILP). A VLIW processor allows programs to explicitly specify instructions to execute in parallel, whereas conventional central processing units (CPUs)... 24 KB (2,975 words) - 19:38, 23 March 2024 |

EOL—End of Line EOM—End of Message EOS—End of Support EPIC—Explicitly Parallel Instruction Computing EPROM—Erasable Programmable Read-Only Memory ERD—Entity–Relationship... 91 KB (6,615 words) - 18:20, 4 May 2024 |

| of parallel computing: bit-level, instruction-level, data, and task parallelism. Parallelism has long been employed in high-performance computing, but... 74 KB (8,564 words) - 00:27, 2 May 2024 |

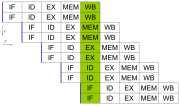

| Superscalar processor (category Parallel computing) very long instruction word (VLIW), explicitly parallel instruction computing (EPIC), simultaneous multithreading (SMT), and multi-core computing. With VLIW... 13 KB (1,537 words) - 22:32, 13 May 2024 |

RS/6000 and, more recently, have contributed to the Explicitly Parallel Instruction Computing (EPIC) computing paradigm used by Intel and HP in the Itanium processors... 20 KB (2,990 words) - 08:01, 2 May 2024 |

Wide-issue (category Parallel computing) determines which instructions are ready and safe to dispatch on each clock cycle. Out-of-order execution Explicitly parallel instruction computing "Scheduling... 1 KB (130 words) - 15:59, 5 February 2021 |

Evolutionary Process for Integrating COTS-Based Systems Explicitly parallel instruction computing, a CPU architecture design philosophy Expansion via Prediction... 6 KB (720 words) - 06:05, 23 April 2024 |

common goal for their work. The terms "concurrent computing", "parallel computing", and "distributed computing" have much overlap, and no clear distinction... 49 KB (5,466 words) - 02:12, 9 May 2024 |

Concurrent computing is a form of computing in which several computations are executed concurrently—during overlapping time periods—instead of sequentially—with... 28 KB (2,908 words) - 23:52, 27 March 2024 |

SSE4 (redirect from Gesher New Instructions) instruction. The parallel operation packs noticeable increases in performance. SSE4.2 introduced new SIMD string operations, including an instruction... 23 KB (1,602 words) - 03:59, 2 May 2024 |

| designed Elbrus-3 computer using an architecture named Explicitly Parallel Instruction Computing (EPIC). From 1992 to 2004, Babayan held senior positions... 5 KB (440 words) - 05:48, 22 March 2024 |

introduced the DirectCompute GPU computing API, released with the DirectX 11 API. Alea GPU, created by QuantAlea, introduces native GPU computing capabilities... 67 KB (6,690 words) - 08:33, 27 February 2024 |

particular tasks. Usually heterogeneity in the context of computing refers to different instruction-set architectures (ISA), where the main processor has... 14 KB (1,547 words) - 12:13, 25 February 2024 |

IA-64 (category Very long instruction word computing) a variation of VLIW design concepts which Intel named explicitly parallel instruction computing (EPIC). Intel's goal was to leverage the expertise HP... 29 KB (3,074 words) - 09:26, 4 April 2024 |

SWAR (category Parallel computing) technique for performing parallel operations on data contained in a processor register. SIMD stands for single instruction, multiple data. Flynn's 1972... 8 KB (1,042 words) - 23:03, 22 February 2024 |

| Computer cluster (redirect from Cluster computing) and scheduled by software. The newest manifestation of cluster computing is cloud computing. The components of a cluster are usually connected to each other... 34 KB (3,747 words) - 08:49, 16 March 2024 |

Vector processor (category Parallel computing) In computing, a vector processor or array processor is a central processing unit (CPU) that implements an instruction set where its instructions are designed... 61 KB (8,578 words) - 08:04, 14 May 2024 |

| Single instruction, multiple data (SIMD) is a type of parallel processing in Flynn's taxonomy. SIMD can be internal (part of the hardware design) and... 32 KB (3,733 words) - 19:39, 3 March 2024 |

| early 90s, HP Labs invented the concept of an Explicitly parallel instruction computing (EPIC) instruction set, which led to the Intel Itanium architecture... 13 KB (1,289 words) - 04:15, 1 May 2024 |

Grid computing is the use of widely distributed computer resources to reach a common goal. A computing grid can be thought of as a distributed system... 46 KB (4,799 words) - 19:56, 26 April 2024 |

Explicit data graph execution, or EDGE, is a type of instruction set architecture (ISA) which intends to improve computing performance compared to common... 19 KB (2,876 words) - 18:09, 4 November 2023 |

| History of general-purpose CPUs (category History of computing hardware) call an explicitly parallel instruction computing (EPIC) design. This design supposedly provides the VLIW advantage of increased instruction throughput... 41 KB (5,590 words) - 08:46, 25 April 2024 |

| science, an interpreter is a computer program that directly executes instructions written in a programming or scripting language, without requiring them... 37 KB (4,547 words) - 11:29, 25 March 2024 |

| Multithreading (computer architecture) (category Parallel computing) to further exploit instruction-level parallelism have stalled since the late 1990s. This allowed the concept of throughput computing to re-emerge from... 13 KB (1,562 words) - 15:53, 3 January 2024 |

Computer performance Supercomputer SIMD Multi-core processor Explicitly parallel instruction computing Simultaneous multithreading Dependability Active redundancy... 9 KB (840 words) - 11:10, 28 April 2022 |