| In computing, multiple instruction, multiple data (MIMD) is a technique employed to achieve parallelism. Machines using MIMD have a number of processors... 8 KB (967 words) - 12:12, 23 May 2023 |

| Single instruction, multiple data (SIMD) is a type of parallel processing in Flynn's taxonomy. SIMD can be internal (part of the hardware design) and it... 32 KB (3,733 words) - 19:39, 3 March 2024 |

different data. With SPMD, tasks can be executed on general purpose CPUs. In SIMD the same operation (instruction) is applied on multiple data to manipulate... 16 KB (2,082 words) - 14:14, 25 January 2024 |

Single instruction, multiple threads (SIMT) is an execution model used in parallel computing where single instruction, multiple data (SIMD) is combined... 7 KB (766 words) - 00:24, 26 January 2024 |

| In computing, multiple instruction, single data (MISD) is a type of parallel computing architecture where many functional units perform different operations... 6 KB (759 words) - 18:41, 25 April 2024 |

but most RISC instruction sets include SIMD or vector instructions that perform the same arithmetic operation on multiple pieces of data at the same time... 34 KB (4,278 words) - 05:44, 2 May 2024 |

multiple dispatch (C++ only permits dynamic single dispatch through use of virtual functions). When working with languages that can discriminate data... 52 KB (5,881 words) - 11:13, 25 April 2024 |

| Parallel computing (redirect from Multiple processing elements) are several different forms of parallel computing: bit-level, instruction-level, data, and task parallelism. Parallelism has long been employed in high-performance... 74 KB (8,564 words) - 00:27, 2 May 2024 |

MMX is a single instruction, multiple data (SIMD) instruction set architecture designed by Intel, introduced on January 8, 1997 with its Pentium P5 (microarchitecture)... 14 KB (1,413 words) - 04:19, 27 March 2024 |

A data dependency in computer science is a situation in which a program statement (instruction) refers to the data of a preceding statement. In compiler... 7 KB (1,129 words) - 16:58, 3 March 2024 |

Multiple sclerosis (MS) is a chronic inflammatory demyelinating disease that affects the central nervous system (CNS). Several therapies for it exist,... 131 KB (14,013 words) - 06:42, 1 April 2024 |

Digital Interface MIMD—Multiple Instruction, Multiple Data MIME—Multipurpose Internet Mail Extensions MIMO—Multiple-Input Multiple-Output MINIX—MIni-uNIX... 91 KB (6,615 words) - 18:20, 4 May 2024 |

Multiprocessing (redirect from Multiple processing units) of instructions in multiple contexts (single instruction, multiple data or SIMD, often used in vector processing), multiple sequences of instructions in... 12 KB (1,504 words) - 20:01, 2 March 2024 |

| Multiple sclerosis can cause a variety of symptoms: changes in sensation (hypoesthesia), muscle weakness, abnormal muscle spasms, or difficulty moving;... 64 KB (7,354 words) - 18:01, 4 May 2024 |

| FR-V (microprocessor) (category Very long instruction word computing) long instruction word (VLIW, Multiple Instruction Multiple Data (MIMD), up to 256 bit) instruction set it additionally uses a 4-way single instruction, multiple... 9 KB (810 words) - 13:35, 16 February 2023 |

Word (computer architecture) (redirect from Data word) the natural unit of data used by a particular processor design. A word is a fixed-sized datum handled as a unit by the instruction set or the hardware... 39 KB (3,619 words) - 02:54, 25 March 2024 |

CPU cache (redirect from Instruction cache) CPUs have a hierarchy of multiple cache levels (L1, L2, often L3, and rarely even L4), with different instruction-specific and data-specific caches at level... 96 KB (13,277 words) - 14:52, 30 April 2024 |

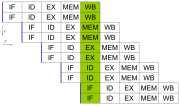

Pipeline (computing) (redirect from Data pipeline) (CPUs) and other microprocessors to allow overlapping execution of multiple instructions with the same circuitry. The circuitry is usually divided up into... 15 KB (2,152 words) - 05:37, 27 December 2023 |

| Multithreading (computer architecture) (category Instruction processing) as instruction-level parallelism. As the two techniques are complementary, they are combined in nearly all modern systems architectures with multiple multithreading... 13 KB (1,562 words) - 15:53, 3 January 2024 |

that the data's memory address is a multiple of the data size. For instance, in a 32-bit architecture, the data may be aligned if the data is stored... 25 KB (3,423 words) - 10:17, 23 February 2024 |

| Central processing unit (redirect from Instruction decoder) every instruction. Using Flynn's taxonomy, these two schemes of dealing with data are generally referred to as single instruction stream, multiple data stream... 100 KB (11,315 words) - 14:15, 3 May 2024 |

Vector processor (section Vector instruction example) implements an instruction set where its instructions are designed to operate efficiently and effectively on large one-dimensional arrays of data called vectors... 61 KB (8,578 words) - 22:41, 17 December 2023 |

device market. Products are based on its Epiphany multi-core multiple instruction, multiple data (MIMD) architecture and its Parallella Kickstarter project... 18 KB (1,462 words) - 00:56, 12 November 2023 |

The descriptors used by the LGDT, LIDT, SGDT and SIDT instructions consist of a 2-part data structure. The first part is a 16-bit value, specifying... 333 KB (15,477 words) - 00:20, 4 May 2024 |

| to detect and mitigate data corruption in CPU caches, CPU buffers and instruction pipelines; an example is Intel Instruction Replay technology, which... 20 KB (2,196 words) - 00:57, 24 September 2023 |

processor chip design company Single instruction, multiple data – Type of parallel processing Single instruction, multiple threads – Execution model used in... 24 KB (2,975 words) - 19:38, 23 March 2024 |