| PowerPC (with the backronym Performance Optimization With Enhanced RISC – Performance Computing, sometimes abbreviated as PPC) is a reduced instruction... 47 KB (5,270 words) - 00:44, 4 May 2024 |

IBM POWER architecture (category Articles with short description) computer (RISC) instruction set architecture (ISA) developed by IBM. The name is an acronym for Performance Optimization With Enhanced RISC. The ISA is... 14 KB (1,751 words) - 20:22, 5 October 2022 |

IBM Power microprocessors (category All articles with dead external links) "POWER" was originally presented as an acronym for "Performance Optimization With Enhanced RISC". The Power line of microprocessors has been used in... 25 KB (2,488 words) - 01:03, 21 December 2023 |

| Acronym (category Articles with short description) "HyperText Transfer Protocol" POWER stands for "Performance Optimization With Enhanced RISC", in which "RISC" stands for "reduced instruction set computer"... 124 KB (14,634 words) - 11:50, 9 April 2024 |

Many companies are offering or have announced RISC-V hardware; open source operating systems with RISC-V support are available, and the instruction set... 130 KB (13,556 words) - 12:29, 7 May 2024 |

| Reduced instruction set computer (redirect from RISC processor) In electronics and computer science, a reduced instruction set computer (RISC) is a computer architecture designed to simplify the individual instructions... 55 KB (6,515 words) - 01:07, 2 May 2024 |

ARM architecture family (redirect from Advanced RISC Machine) as arm, formerly an acronym for Advanced RISC Machines and originally Acorn RISC Machine) is a family of RISC instruction set architectures (ISAs) for... 137 KB (13,383 words) - 11:23, 6 May 2024 |

optimizations could be performed. Because of these factors, optimization rarely produces "optimal" output in any sense, and in fact, an "optimization"... 42 KB (5,670 words) - 21:35, 23 March 2024 |

| Pentium (original) (category Articles with short description) cope with the complicated x86 encodings in a pipelined fashion. Just like the i486, the Pentium used both an optimized microcode system and RISC-like... 36 KB (3,478 words) - 13:55, 9 May 2024 |

Complex instruction set computer (category Articles with short description) reduced instruction set computer (RISC) and has therefore become something of an umbrella term for everything that is not RISC,[citation needed] where the typical... 15 KB (1,971 words) - 15:45, 19 January 2024 |

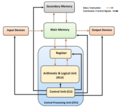

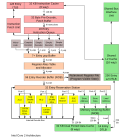

| Computer architecture (category Articles with short description) to one of three subsets of the RISC CPU instructions provided by PowerPC RISC Processors. The UISA subset, are those RISC instructions of interest to application... 26 KB (3,230 words) - 21:29, 13 April 2024 |

List of MediaTek systems on chips (category Articles with short description) Flagship Smartphone Performance with Dimensity 9300+ SoC". MediaTek. Hsinchu, Taiwan. May 7, 2024. Retrieved May 7, 2024. "MediaTek MT8312 RISC Multi-core Application... 105 KB (2,159 words) - 11:44, 9 May 2024 |

loop nest optimization (LNO) is an optimization technique that applies a set of loop transformations for the purpose of locality optimization or parallelization... 16 KB (2,369 words) - 07:52, 12 November 2023 |

Microcode (category Articles with short description) California, Berkeley, that introduced the term RISC. The industry responded to the concept of RISC with both confusion and hostility, including a famous... 73 KB (8,710 words) - 17:45, 24 April 2024 |

P6 (microarchitecture) (redirect from Intel Enhanced Pentium M (microarchitecture)) processors dynamically translate IA-32 instructions into sequences of buffered RISC-like micro-operations, then analyze and reorder the micro-operations to detect... 15 KB (1,545 words) - 13:42, 23 March 2024 |

| Microarchitecture (category Articles with short description) the complexity of implementing high-performance devices. The prominent strategy, used to develop the first RISC processors, was to simplify instructions... 27 KB (3,571 words) - 14:00, 11 April 2024 |

| Android 10 (category Articles with short description) Edition has performance improvements, with Google stating that apps would launch 10% quicker than on Pie. In 2021, Android 10 was ported to the RISC-V architecture... 35 KB (2,961 words) - 14:31, 7 May 2024 |

AES instruction set (category Articles with short description) Exynos 3 series onwards Whilst the RISC-V architecture does not include AES-specific instructions, a number of RISC-V chips include integrated AES co-processors... 24 KB (2,114 words) - 22:03, 18 March 2024 |

| Godot (game engine) (category All articles with dead external links) version after several beta builds and bug fixes. It enhanced graphics quality, rendering optimization techniques, and added accessibility features. This... 50 KB (4,051 words) - 16:46, 8 May 2024 |

List of Intel CPU microarchitectures (category Articles with short description) optimization model and Template:Intel processor roadmap. 8086 first x86 processor; initially a temporary substitute for the iAPX 432 to compete with Motorola... 50 KB (2,873 words) - 14:22, 9 April 2024 |

Self-tuning (category Articles with Russian-language sources (ru)) (Self Tuning Linear Algebra Software for RISC) MILEPOST GCC (Machine learning based self-tuning compiler) Performance benefits can be substantial. Professor... 7 KB (1,282 words) - 18:54, 9 February 2024 |

| VAX (category Articles with short description) DEC's product offerings, the VAX architecture was eventually superseded by RISC technology. In 1989 DEC introduced a range of workstations and servers that... 32 KB (3,029 words) - 19:49, 16 February 2024 |

| Central processing unit (redirect from Performance Counter Monitor) simultaneously. This section describes what is generally referred to as the "classic RISC pipeline", which is quite common among the simple CPUs used in many electronic... 100 KB (11,315 words) - 14:15, 3 May 2024 |

| SPARC (category Articles with short description) (RISC) instruction set architecture originally developed by Sun Microsystems. Its design was strongly influenced by the experimental Berkeley RISC system... 74 KB (6,095 words) - 05:57, 4 April 2024 |

| Single instruction, multiple data (category Articles with short description) to meet the demand. Hewlett-Packard introduced MAX instructions into PA-RISC 1.1 desktops in 1994 to accelerate MPEG decoding. Sun Microsystems introduced... 32 KB (3,733 words) - 19:39, 3 March 2024 |

| HP-UX (category Articles with short description) proprietary FOCUS architecture, and later HP 9000 Series models based on HP's PA-RISC instruction set architecture. HP-UX was the first Unix to offer access-control... 27 KB (2,953 words) - 22:53, 18 April 2024 |

| VIA C3 (category Articles with short description) from the original RISC advocates, who stated a smaller set of instructions, better optimized, would deliver faster overall CPU performance. As it makes heavy... 12 KB (1,177 words) - 01:39, 16 April 2024 |

| Centaur Technology (category Articles with short description) the original RISC advocates, who claim that a smaller set of instructions, better optimized, can deliver faster overall CPU performance. The C3 design... 13 KB (1,263 words) - 02:35, 1 May 2024 |

Advanced Vector Extensions (category Articles with short description) is a new extension. It is not focused on vector computation, but provides RISC-like extensions to the x86-64 architecture by doubling the number of general... 53 KB (4,309 words) - 09:53, 8 May 2024 |

| X86 (category Articles with short description) in high-performance computing clusters and powerful desktop workstations. The aged 32-bit x86 was competing with much more advanced 64-bit RISC architectures... 104 KB (10,773 words) - 01:35, 2 May 2024 |