خودکارسازی طراحی الکترونیکی - ویکیپدیا، دانشنامهٔ آزاد

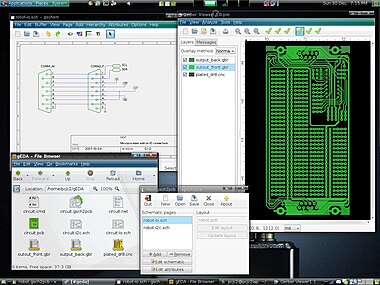

خودکارسازی طراحی الکترونیکی (EDA) ، که به عنوان طراحی الکترونیکی به کمک رایانه (ECAD) نیز شناخته میشود،[۱] دسته ای از ابزارهای نرمافزاری برای طراحی سیستمهای الکترونیکی مانند مدارهای مجتمع و بردهای مدار چاپی است. این ابزارها در یک جریان طراحی با یکدیگر کار میکنند که طراحان تراشه از آن برای طراحی و تجزیه و تحلیل کامل تراشههای نیمه هادی استفاده میکنند. از آنجا که یک تراشه نیمه هادی مدرن میتواند میلیاردها جزء داشته باشد، ابزارهای EDA برای طراحی آنها ضروری است. این مقاله بهطور خاص EDA را با توجه به مدارهای مجتمع (IC) توصیف میکند.

تاریخچه[ویرایش]

روزهای نخست[ویرایش]

پیش از توسعه EDA، مدارهای مجتمع به صورت دستی طراحی و تنظیم میشدند. برخی از فروشگاههای پیشرفته از نرمافزار هندسی برای تولید نوارهایی برای یک فتوپلاتر Gerber استفاده میکردند، که مسئول تولید یک عکس با نوردهی تک رنگ است، اما حتی آنها هم ضبطهای دیجیتالی از اجزای ترسیم شده مکانیکی را کپی میکردند. این فرایند اساساً گرافیکی بود و تبدیل آن از الکترونیک به گرافیک به صورت دستی انجام میشد. مشهورترین شرکت از این دوران Calma بود که قالب GDSII آن امروزه همچنان مورد استفاده است. در اواسط دهه ۱۹۷۰، توسعه دهندگان علاوه بر پیش نویس کردن، طراحی مدار را به صورت خودکار آغاز کردند و اولین ابزارهای قراردهی و مسیریابی توسعه یافتند. با وقوع این امر، مقالات کنفرانس اتوماسیون طراحی، اکثریت پیشرفتهای آن زمان را دربرمی گرفت.

دوره بعدی به دنبال انتشار "مقدمه ای بر سیستمهای VLSI " توسط کارور مید و لین کانوی در سال ۱۹۸۰ آغاز شد. این متن پیشگامانه طرفدار طراحی تراشه با زبانهای برنامهنویسی است که به سیلیکون وارد میشوند. نتیجه فوری افزایش قابل توجه پیچیدگی تراشههای قابل طراحی، با دسترسی بهتر به ابزارهای تأییدکننده طراحی که از شبیهسازی منطقی استفاده میکردند، بود. اغلب چیدمان تراشهها سادهتر بود و احتمال عملکرد صحیح آنها بیشتر بود، زیرا امکان شبیهسازی دقیق تر طرحهای آنها پیش از ساخت فراهم میشد. اگرچه زبانها و ابزارها تکامل یافتهاند، اما این رویه کلی در تعیین رفتار مطلوب در یک زبان برنامهنویسی متنی و نیز اجازه دادن به ابزارها برای کسب طراحی فیزیکی دقیق، امروزه اساس طراحی IC دیجیتال است.

اولین ابزارهای EDA به صورت آکادمیک تولید شدند. یکی از مشهورترینها "Berkeley VLSI Tools Tarball" بود، مجموعه ای از ابزارهای یونیکس که برای طراحی سیستمهای اولیه VLSI استفاده میشد. هنوز هم بهطور گستردهای استفاده میشود که Espresso heuristic logic minimizer، مسئول کاهش پیچیدگی مدار و Magic، یک پلت فرم طراحی به کمک کامپیوتر است. یکی دیگر از تحولات تعیینکننده تشکیل MOSIS، کنسرسیومی از دانشگاهها و تولیدکنندگان بود که با تولید مدارهای مجتمع واقعی راهی ارزان برای آموزش دانشجویان طراحی تراشه را ایجاد کرد. مفهوم بنیادی استفاده از فرایندهای آی سی مطمئن، کم هزینه و نسبتاً کم فناوری و بستهبندی تعداد زیادی پروژه در هر ویفر بود که چندین نسخه تراشه از هر پروژه حفظ شود. سازندگان همکاری یا ویفرهای فرآوری شده را اهدا میکردند یا آنها را با هزینه تمام شده میفروختند. همانطور که آنها این برنامه را برای رشد بلند مدت خود مفید میدانستند.

تولد EDA تجاری[ویرایش]

سال ۱۹۸۱ آغاز EDA به عنوان یک صنعت را رقم زد. برای سالها، شرکتهای الکترونیکی بزرگتر، مانند هیولت پاکارد، Tektronix و اینتل، از EDA را به نحوی درونی اتخاذ کرده بودند، مدیران و توسعه دهندگان شروع به خروج از این شرکتها کردند تا بر EDA به عنوان یک تجارت تمرکز کنند. سیستمهای Daisy , Mentor Graphics و Valid Logic Systems همه در این زمان تأسیس شدند و در مجموع به عنوان DMV شناخته میشوند. در سال ۱۹۸۱، وزارت دفاع ایالات متحده علاوه بر این بودجه VHDL را به عنوان زبان توصیف سختافزار آغاز کرد. باگذشت چند سال، بسیاری از شرکتها در EDA مهارت داشتند که هریک تأکیدی اندکی متفاوت داشتند.

اولین نمایشگاه تجاری EDA در کنفرانس خودکارسازی طراحی در سال ۱۹۸۴ برگزار شد و در سال ۱۹۸۶، Verilog، یکی دیگر از زبانهای طراحی سطح بالا و محبوب، ابتدا توسط Gateway Design Automation به عنوان زبان توصیف سختافزار معرفی شد. شبیهسازها به سرعت این معرفیها را دنبال کردند و اجازه شبیهسازی مستقیم تراشهها و مشخصات اجرایی را صادر کردند. در طی چندین سال، برای انجام logic synthesis. ، خطوط انتهایی ساخته شدند.

وضعیت فعلی[ویرایش]

جریانهای دیجیتال کنونی بسیار پیمانه ای هستند که قسمتهای جلویی آنها توصیفات استانداردی را تولید میکنند که در فراخوانی واحدهایی مشابه سلولها بدون در نظر گرفتن فناوری فردی آنها جمع میشوند. سلولها ابه کمک استفاده از یک فناوری مدار مجتمع خاص، منطق یا سایر توابع الکترونیکی را پیادهسازی میکنند. سازندگان بهطور کلی مجموعه ای از اجزا را برای فرایندهای تولید خود، با مدلهای شبیهسازی متناسب با ابزارهای شبیهسازی استاندارد، فراهم میکنند. ابزارهای آنالوگ EDA به مراتب کمتر پیمانه ای هستند، از آنجا که توابع بیشتری لازم است، آنها با یکدیگر ارتباط بیشتری برقرار میکنند و اجزا بهطور کلی، کمتر ایدئال هستند.

اهمیت EDA برای الکترونیک با مقیاس گذاری پیوسته فناوری نیمه هادی به سرعت افزایش یافتهاست. برخی از کاربران اپراتورهای ریختهگری هستند که با استفاده از امکانات ساخت نیمه هادی ("fabs") و اشخاص دیگری که مسئول استفاده از شرکتهای خدمات طراحی فناوری هستند و از نرمافزار EDA برای ارزیابی یک طرح ورودی برای آمادگی تولید استفاده میکنند. ابزارهای EDA همچنین برای برنامهنویسی کارایی طراحی در FPGA یا آرایههای دروازه قابل برنامهریزی زمینه ای، طرحهای مدار مجتمع قابل تنظیم استفاده میشوند.

تمرکز نرمافزار[ویرایش]

طراحی[ویرایش]

جریان طراحی در درجه اول از طریق چندین مولفه اصلی و اولیه مشخص میشود؛ که شامل:

- پیوند سطح بالا (علاوه بر این به عنوان پیوند رفتاری الگوریتمی پیوند رفتاری شناخته میشود) – شرح طراحی سطح بالا (به عنوان مثال در C / C ++) به RTL یا سطح انتقال ثبات تبدیل میشود، مسئول نمایش مدارها از طریق استفاده از ارتباطات میان ثباتها.

- پیوند منطق – ترجمه توصیف طراحی RTL (به عنوان مثال با Verilog یا VHDL نوشته شده) به یک شبکه لیست گسسته یا نمایش دروازههای منطقی.

- ضبط شماتیک – برای سلول استاندارد دیجیتال، آنالوگ، RF مانند Capture CIS در Orcad توسط Cadence و ISIS در Proteus.[نیازمند شفافسازی]

- طرح بندی – معمولاً طرح بندی برمبنای شماتیک، مانند طرح بندی در Orcad توسط Cadence , ARES در Proteus

شبیهسازی[ویرایش]

- شبیهسازی ترانزیستور - شبیهسازی ترانزیستور سطح پایین از یک رفتار شماتیک / ساختاری، دقیق در سطح دستگاه.

- شبیهسازی منطقی - شبیهسازی دیجیتالی رفتار دیجیتالی RTL یا gate-netlist (بولی ۰/۱)، دقیق در سطح بولی.

- شبیهسازی رفتاری - شبیهسازی سطح بالا از عملکرد معماری یک طرح، دقیق در سطح چرخه یا سطح رابط.

- شبیهسازی سختافزار - استفاده از سختافزار مخصوص برای تقلید نمودن از منطق طرح پیشنهاد شده. برخی اوقات میتواند به جای یک تراشه که هنوز درحال ساخت است، به سیستم متصل شود. این را شبیهسازی در مدار می نامند.

- Technology CAD فناوری فرایند بنیادی را شبیهسازی و تحلیل میکند. ویژگیهای الکتریکی دستگاهها مستقیماً از فیزیک دستگاه حاصل میشود.

- حل کنندههای میدان الکترومغناطیسی، یا فقط حل کنندههای میدان، معادلات ماکسول را مستقیماً برای موارد مورد نظر در طراحی IC و PCB حل میکنند. آنها به کندتر اما دقیق تر از استخراج ساختار در بالا معروف هستند.

تحلیل و تأیید[ویرایش]

- تأیید کارایی

- تأیید عبور از دامنه ساعت (بررسی CDC): شبیه لاینتینگ است، اما این چکها / ابزارها در شناسایی و گزارش مشکلات محتمل مانند از دست دادن دادهها، متا ثبات به دلیل استفاده از چندین دامنه ساعت در طراحی مهارت دارند.

- تأیید رسمی، همچنین بررسی مدل: تلاش میشود با روشهای ریاضی ثابت شود که سیستم دارای ویژگیهای مورد نظر خاصی است و برخی از اثرات نامطلوب (مانند بنبست)که نمیتواند رخ دهد.

- بررسی معادل بودن: مقایسه الگوریتمی بین توصیف RTL یک تراشه و net-gate پیوند شده برای اطمینان از همارزی عملکرد در سطح منطقی.

- تجزیه و تحلیل زمان استاتیک: تجزیه و تحلیل زمانبندی مدار به روشی مستقل از ورودی، بنابراین یافتن بدترین حالت از همه ورودیهای ممکن.

- تأیید فیزیکی، PV: بررسی اینکه آیا یک طرح از نظر فیزیکی قابل تولید است یا خیر، و اینکه تراشههای حاصل، نقص فیزیکی جلوگیری از عملکرد نخواهند داشت و مشخصات اصلی را خواهند داشت.

آمادهسازی ساخت[ویرایش]

- ماسک آمادهسازی دادهها یا MDP - نسل واقعی لیتوگرافی photomasks، استفاده برای تولید فیزیکی تراشه.

- روشهای افزایش وضوح یا RET - روشهایی برای افزایش کیفیت فوتوماسک نهایی.

- اصلاح مجاورت نوری یا OPC - جبران جلو برای اثرات پراش و تداخل که بعداً هنگام تولید تراشه با استفاده از این ماسک رخ میدهد.

- تولید ماسک - تولید تصویر ماسک مسطح از طراحی سلسله مراتبی.

- تولید الگوی آزمون خودکار یا ATPG - تولید دادههای الگو بهطور سیستماتیک برای تمرین هرچه بیشتر دروازههای منطقی و سایر اجزای ممکن.

- ساخته شده در خودآزمایی یا BIST - نصب کنترلکنندههای شامل خود برای آزمایش خودکار منطق یا حافظه) ساختار در طراحی

ایمنی عملکرد[ویرایش]

- تحلیل ایمنی عملکردی، محاسبه سیستماتیک شکست در نرخ زمان (FIT) و معیارهای پوشش تشخیصی برای طراحیها به منظور تأمین الزامات انطباق برای یکپارچه شدن سطح ایمنی مورد نظر.

- با استفاده از پیوند ایمنی عملکردی، به عناصر ساختار یافته (ماژولها، RAMها، ROMها، پروندههای ثبتی، FIFOها) پیشرفتهای قابلیت اطمینان اضافه میشود تا تشخیص خطا / تحمل خطا را بهبود بخشد. این موارد شامل (محدود نمیشود)، اضافه شدن کدهای تشخیص خطا و / یا تصحیح (Hamming)، منطق اضافی برای شناسایی خطا و تحمل خطا (دوبرابر/ سه برابر) و بررسی پروتکل (جفت شدن رابط، تراز بندی آدرس، تعداد ضربانها)

- تأیید ایمنی عملکرد، اجرای یک کمپین خطا، از جمله درج خطا در طراحی و تأیید اینکه مکانیسم ایمنی به روشی مناسب برای خطاهایی که پوشانده تلقی میشود، واکنش نشان میدهد.

شرکتها[ویرایش]

شرکتهای قدیمی[ویرایش]

سرمایه بازار و نام شرکت تا تاریخ دسامبر ۲۰۱۱[بروزرسانی]:[۲]

- ۵٫۷۷ میلیارد دلار[۳] - Synopsys

- ۴٫۴۶ میلیارد دلار[۴] - Cadence

- ۲٫۳۳ میلیارد دلار - Mentor Graphics

- ۵۰۷ میلیون دلار - اتوماسیون طراحی ماگما؛ Synopsys ماگما را در فوریه ۲۰۱۲ خریداری کرد[۵][۶]

- ۶٫۴۴ میلیارد دلار NT - SpringSoft؛ سینوپسیس SpringSoft را در اوت ۲۰۱۲ خریداری کرد

- ۱۱٫۹۵ میلیارد پوند - Zuken Inc.

توجه: EEsof احتمالاً باید در این لیست باشد،[۷] اما کلاهک بازار ندارد زیرا بخش EDA Keysight است.

مالکیت[ویرایش]

بسیاری از شرکتهای EDA شرکتهای کوچک با نرمافزار یا دیگر فناوریها را خریداری میکنند که میتواند با تجارت مرکزی آنها متناسب باشد.[۸] بیشتر رهبران بازار ادغام بسیاری از شرکتهای کوچکتر هستند و این گرایش توسط شرکتهای نرمافزاری به طراحی ابزارهایی به عنوان لوازم جانبی کمک میکند که بهطور طبیعی با مجموعه برنامههای فروشنده بزرگتر روی مدارهای دیجیتال تناسب دارند. بسیاری از ابزارهای جدید دارای طراحی آنالوگ و سیستمهای ترکیبی هستند.[۹] این اتفاق به دلیل گرایش به قرار دادن کل سیستمهای الکترونیکی روی یک تراشه رخ میدهد.

جستارهای وابسته[ویرایش]

منابع[ویرایش]

- ↑ "About the EDA Industry". Electronic Design Automation Consortium. Archived from the original on August 2, 2015. Retrieved 29 July 2015.

- ↑ Company Comparison - Google Finance. Google.com. Retrieved on 2013-08-10.

- ↑ Synopsys, Inc.: NASDAQ:SNPS quotes & news - Google Finance. Google.com (2013-05-22). Retrieved on 2013-08-10.

- ↑ CDNS Key Statistics | Cadence Design Systems, Inc. Stock - Yahoo! Finance. Finance.yahoo.com. Retrieved on 2013-08-10.

- ↑ Dylan McGrath (30 Nov 2011). "Synopsys to buy Magma for $507 million". EETimes.

- ↑ "Synopsys to Acquire Magma Design Automation".

- ↑ "Agilent EEsof EDA – Part I".

- ↑ Kirti Sikri Desai (2006). "EDA Innovation through Merger and Acquisitions". EDA Cafe. Retrieved March 23, 2010.

- ↑ "Semi Wiki:EDA Mergers and Acquisitions Wiki". SemiWiki.com (به انگلیسی). 2011-01-16. Archived from the original on 3 April 2019. Retrieved 2019-04-03.

French

French Deutsch

Deutsch