ردیابی حافظه نهان - ویکیپدیا، دانشنامهٔ آزاد

در معماری رایانه ، حافظه پنهان ردیابی یک حافظه نهان سیپییو تخصصی است که جریان پویای دستورالعمل های معروف به ردیابی را ذخیره می کند . با ذخیره ردیابی دستورالعمل هایی که قبلاً واکشی و رمزگشایی شدهاند ، به افزایش پهنای باند واکشی دستورالعمل و کاهش مصرف برق (در مورد اینتل پنتیوم ۴ ) کمک می کند. [۱] پردازنده ردیابی [۲] معماری است که در اطراف حافظه پنهان ردیابی طراحی شده است و دستورالعمل ها را در دانه دانه بودن سطح ردیابی پردازش می کند. نظریه رسمی ریاضی ردیابی توسط مونوئیدهای ردیابی توصیف می شود.

زمینه[ویرایش]

اولین انتشار علمی حافظه پنهان ردیابی "Trace Cache: رویکردی با تأخیر کم برای واکشی دستورالعمل پهنای باند" بود. [۱] این مقاله که به طور گسترده مورد تأیید قرار گرفته است توسط اریک روتنبرگ ، استیو بنت و جیم اسمیت در کنفرانس بینالمللی سمپوزیوم بینالمللی ریز معماری (MICRO) در سال 1996 ارائه شد. انتشار قبلی ، اختراع ثبت شده 5381533 ایالات متحده [۳] توسط الکس پِلگ و یوری وایزر از اینتل ، "حافظه پنهان پویای دستورالعمل جریان پویا است که در اطراف بخشهای ردیابی مستقل از خط آدرس مجازی سازمان یافته است" ، ادامه برنامه ای که در سال 1992 ثبت شد ، بعداً رها شد.

ضرورت[ویرایش]

پردازنده های سوپراسکالر گسترده تر ، برای عملکرد بالاتر ، دستورالعمل های متعددی را می خواهند که در یک چرخه واحد واکشی شوند. دستورالعمل های واکشی به دلیل دستورالعمل های شاخه و پرش ،همیشه در مکان های حافظه مجاور ( بلوک پایه ) نیستند. بنابراین پردازنده ها برای واکشی و هم ترازی چنین دستورالعمل هایی از بلوک های اساسی غیرهمجوار به پشتیبانی منطقی و سخت افزاری اضافی نیاز دارند. اگر چندین شاخه به عنوان عدم گرفته پیش بینی شده باشد ، پردازنده ها می توانند دستورالعمل ها را از چندین بلوک اساسی مجاور در یک چرخه دریافت کنند. با این حال ، اگر هر یک از شاخه ها به عنوان گرفته شده پیش بینی شده باشد ، پردازنده باید دستورالعمل هایی را از مسیر طی شده در همان چرخه دریافت کند. این قابلیت واکشی پردازنده را محدود می کند.

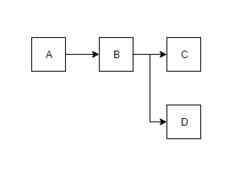

این چهار بلوک اساسی ( A ، B ، C ، D ) را همانطور که در شکل نشان داده شده است در نظر بگیرید که مربوط به یک حلقه ساده در صورت وجود است. این بلوک ذخیره خواهد شد پارگی به عنوان ABCD در حافظه است. اگر پیش بینی شود D گرفته نشده است ، واحد واکشی می تواند بلوک های اصلی A ، B ، C که به طور همزمان قرار می گیرند ، واکشی کند. با این حال ، اگر پیش بینی D گرفته شود ، واحد واکشی باید A ، B ، D که به طور غیر هم پیوسته قرار می گیرند ، واکشی کند. از این رو ، واکشی این بلوک ها که به طور ناپیوسته در یک چرخه قرار می گیرند بسیار دشوار خواهد بود. بنابراین ، در چنین موقعیت هایی حافظه پنهان ردیابی به پردازنده کمک می کند.

حافظه نهان ردیابی پس از واکشی ، دستورالعمل ها را به ترتیب پویای خود ذخیره می کند. هنگامی که این دستورالعمل ها مجدداً مشاهده می شوند ، حافظه پنهان ردیابی به واحد واکشی دستورالعمل پردازنده اجازه می دهد تا چندین بلوک اساسی را بدون نگرانی از شاخه های موجود در جریان اجرا ، از آن دریافت کند. دستورالعمل ها یا پس از رمزگشایی یا پس از منقضی شدن ، در حافظه پنهان ردیابی ذخیره می شوند. اگرچه توالی دستورالعمل اگر فقط پس از مرحله رمزگشایی ذخیره شود ، حدسی است.

ساختار ردیابی[ویرایش]

یک ردیابی که توالی دستورالعمل پویا نیز نامیده می شود ، ورودی در حافظه پنهان ردیابی است. با حداکثر تعداد دستورالعمل و حداکثر بلوک های اساسی می تواند مشخص شود . ردیابی ها می توانند در هر دستورالعمل پویا شروع شوند. چندین ردیابی می تواند دارای همان دستورالعمل شروع ، یعنی همان اولین شمارنده برنامه (PC) و دستورالعمل های مختلف از بلوک های مختلف به عنوان نتایج شاخه داشته باشد. برای شکل بالا ، ABC و ABD ردیابی معتبری هستند. هر دو با یک PC (آدرس A) شروع می شوند و طبق پیش بینی D ، بلوک های اساسی مختلفی دارند.

ردیابی ها معمولاً در صورت وقوع یکی از موارد زیر خاتمه می یابند:

- ردیابی با حداکثر تعداد مجاز دستورالعمل پر شده

- ردیابی دارای حداکثر بلوک های اساسی مجاز است

- دستورالعمل بازگشت

- شاخه های غیرمستقیم

- تماس های سیستمی

اطلاعات کنترل ردیابی[ویرایش]

یک ردیابی دارای اطلاعات زیر خواهد بود:

- اولین PC - PC اولین دستورالعمل در ردیابی

- نشانگر شاخه - ( حداکثر بلوک های اساسی -1 ) پیش بینی شاخه

- ماسک شاخه - تعداد شاخه های موجود در ردیابی و اینکه آیا ردیابی به شاخه ختم می شود یا خیر

- ردیابی از طریق سقوط -PC بعدی اگر آخرین دستورالعمل شاخه ای گرفته نشود یا شاخه ای نباشد

- هدف ردیابی - آدرس هدف گرفته شده آخرین شاخه

طراحی ردیابی حافظه نهان[ویرایش]

در اینجا عواملی ذکر شده است که باید هنگام طراحی حافظه پنهان مورد بررسی قرار گیرند.

- خط مشی های انتخاب ردیابی - حداکثر تعداد دستورالعمل ها و حداکثر بلوک های اساسی در ردیابی

- حافظه نهان سیپییو - تعداد راههایی که یک حافظه پنهان می تواند داشته باشد

- روش نمایه سازی حافظه پنهان - الحاق یا XOR با بیت های PC

- تداعی کننده مسیر - ردیابی هایی که با همان PC شروع می شوند اما با بلوک های مختلف متفاوت می توانند در مجموعه های مختلف نگاشت شوند

- ردیابی گزینه های پر کردن حافظه پنهان -

- بعد از مرحله رمزگشایی (حدس و گمان)

- بعد از مرحله منقضی شدن

حافظه پنهان در مسیر مهم واکشی دستورالعمل نیست [۴]

منطق اصابت / خطا[ویرایش]

خطوط ردیابی بر اساس PC اولین دستورالعمل موجود در ردیابی و مجموعه پیش بینی های شاخه ، در حافظه پنهان ردیابی ذخیره می شوند. این امکان را برای ذخیره مسیرهای ردیابی مختلف فراهم می کند که از همان آدرس شروع می شوند ، هر کدام نتایج مختلف شاخه را نشان می دهند. این روش برچسب گذاری به ایجاد ارتباط مسیر به حافظه پنهان ردیابی کمک می کند. روش دیگر می تواند شامل تنها نگهداری اولین PC به عنوان برچسب در حافظه پنهان باشد. در مرحله واکشی دستورالعمل یک خط لوله ، PC فعلی به همراه مجموعه ای از پیش بینی های شاخه در حافظه پنهان ردیابی برای ضربه بررسی می شود . اگر ضربه ای ایجاد شود ، یک خط ردیابی برای واحد واکشی ارائه می شود که برای این دستورالعمل ها نیازی به رفتن به حافظه پنهان معمولی یا حافظه نیست. حافظه پنهان ردیابی به تغذیه واحد واکشی ادامه می دهد تا زمانی که خط ردیابی به پایان برسد یا اینکه پیشبینیکننده پرش اشتباهی در خط لوله وجود داشته باشد. در صورت عدم وجود ، ردیابی جدید شروع به ساخت می کند.

حافظه پنهان اجرای پنتیوم ۴ عملیات خرد حاصل از رمزگشایی دستورالعمل های x86 را ذخیره می کند ، همچنین عملکرد حافظه پنهان ریز عملکرد را فراهم می کند. با این وجود ، دفعه بعدی که یک دستورالعمل مورد نیاز است ، نیازی به رمزگشایی مجدد در ریز عملیات نیست. [۵]

معایب[ویرایش]

معایب حافظه پنهان ردیابی عبارتند از:

- ذخیره دستورالعمل اضافی بین ردیابی حافظه پنهان و حافظه پنهان دستورالعمل و در داخل ردیابی حافظه پنهان. [۶]

- عدم کارایی برق و پیچیدگی سخت افزار [۴]

ردیابی حافظه پنهان[ویرایش]

اینتل در حافظه پنهان L1 پردازنده های NetBurst ، حافظه پنهان ردیابی اجرا را در خود جای داده است. [۷] [۸] این عملیات رمزگشایی شده را ذخیره می کند ، بنابراین هنگام اجرای یک دستورالعمل جدید ، به جای واکشی و رمزگشایی مجدد دستورالعمل ، پردازنده مستقیماً از ردیابی حافظه پنهان به ریز رمزگشایی های رمزگشایی شده دسترسی پیدا می کند و در نتیجه باعث صرفه جویی در وقت قابل توجهی می شود. علاوه بر این ، ریز op ها در مسیر پیش بینی شده خود در حافظه پنهان می شوند ، به این معنی که وقتی دستورالعمل ها توسط CPU از حافظه پنهان واکشی می شوند ، آنها از قبل به ترتیب صحیح اجرا وجود دارند. اینتل بعداً مفهومی مشابه اما ساده تر با سندی بریج به نام حافظه پنهان کوچک (UOP cache) ارائه داد.

جستارهای وابسته[ویرایش]

منابع[ویرایش]

- ↑ ۱٫۰ ۱٫۱ Rotenberg, Eric; Bennett, Steve; Smith, James E.; Rotenberg, Eric (1996-01-01). "Trace Cache: a Low Latency Approach to High Bandwidth Instruction Fetching". In Proceedings of the 29th International Symposium on Microarchitecture: 24–34.

- ↑ Eric Rotenberg, Quinn Jacobson, Yiannakis Sazeides, and James E. Smith. Trace Processors. Proceedings of the30th IEEE/ACM International Symposium on Microarchitecture (MICRO-30), pp. 138-148, December 1997

- ↑ Peleg, Alexander; Weiser, Uri (Jan 10, 1995), Dynamic flow instruction cache memory organized around trace segments independent of virtual address line, retrieved 2016-10-18

- ↑ ۴٫۰ ۴٫۱ Leon Gu; Dipti Motiani (October 2003). "Trace Cache" (PDF). Retrieved2013-10-06.

- ↑ Agner Fog (2014-02-19). "The microarchitecture of Intel, AMD and VIA CPUs: An optimization guide for assembly programmers and compiler makers" (PDF). agner.org. Retrieved 2014-03-21.

- ↑ Co, Michele. "Trace Cache". www.cs.virginia.edu. Retrieved 2016-10-21.

- ↑ [۱]

- ↑ https://web.archive.org/web/20160306140603/http://www.xbitlabs.com/articles/cpu/print/replay.html

French

French Deutsch

Deutsch